NanoAmp Solutions, Inc. 1982 Zanker Road, San Jose, CA 95112 ph: 408-573-8878, FAX: 408-573-8877 www.nanoamp.com

# *EM128L08 Family* 128Kx8 Bit Ultra-Low Power Asynchronous Static RAM

# Overview

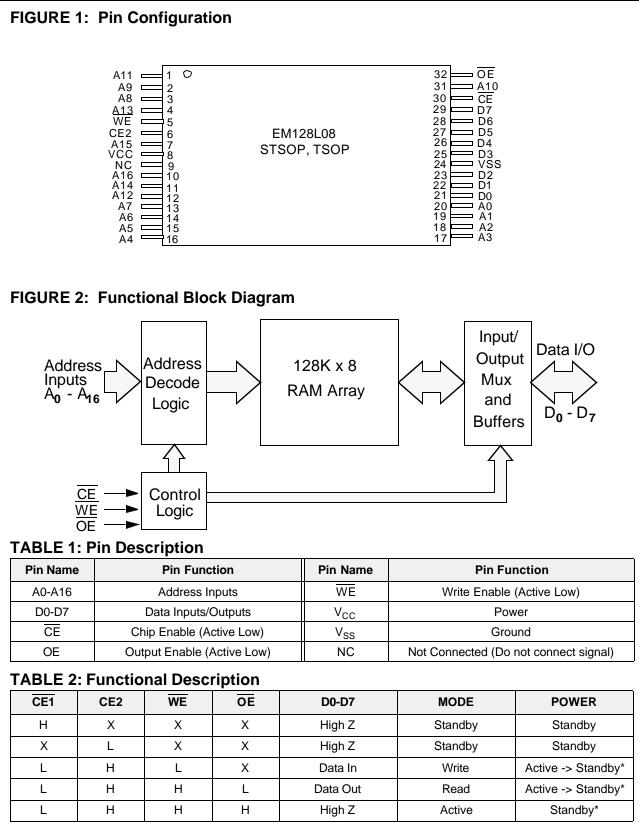

The EM128L08 is an integrated memory device containing a low power 1 Mbit Static Random Access Memory organized as 131,072 words by 8 bits. The device is fabricated using NanoAmp's advanced CMOS process and high-speed/lowpower circuit technology. This device is designed for very low voltage operation making it quite suitable for battery powered devices. It is also designed for both very low operating and standbycurrents. The device pinout is compatible with other standard 128Kx8 SRAMs.

## Features

- Wide Voltage Range: 2.3 to 3.6 Volts

- Extended Temperature Range: -40 to +85 °C

- Fast Cycle Time: T<sub>ACC</sub> < 55 ns @ 3.0V

</li>

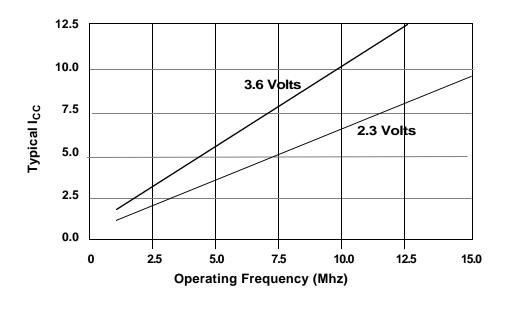

- Very Low Operating Current: I<sub>CC</sub> < 10 mA typical at 3V, 10 Mhz

- Very Low Standby Current: I\_{SB} < 10  $\mu A @~55 ~^{o}C$

- 32-Pin TSOP, STSOP, Packages Available

# FIGURE 1: Typical Operating Current Curves

\*The device will consume active power in this mode whenever addresses are changed

## TABLE 3: Absolute Maximum Ratings\*

| Item                                                    | Symbol              | Rating                       | Unit |

|---------------------------------------------------------|---------------------|------------------------------|------|

| Voltage on any pin relative to $V_{SS}$                 | V <sub>IN,OUT</sub> | –0.3 to V <sub>CC</sub> +0.3 | V    |

| Voltage on $V_{\rm CC}$ Supply Relative to $V_{\rm SS}$ | V <sub>CC</sub>     | -0.3 to 4.0                  | V    |

| Power Dissipation                                       | PD                  | 500                          | mW   |

| Storage Temperature                                     | T <sub>STG</sub>    | -40 to 125                   | °C   |

| Operating Temperature                                   | T <sub>A</sub>      | -40 to +85                   | °C   |

| Soldering Temperature and Time                          | T <sub>SOLDER</sub> | 260 °C, 10sec(Lead only)     | °C   |

\* Stresses greater than those listed above may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **TABLE 4: Operating Characteristics (Over specified Temperature Range)**

| Item                                                        | Symbol           | Test Conditions                                                                                       | Min                  | Тур | Max                  | Unit |

|-------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------|----------------------|-----|----------------------|------|

| Supply Voltage                                              | V <sub>CC</sub>  |                                                                                                       | 2.3                  |     | 3.6                  | V    |

| Data Retention Voltage                                      | V <sub>DR</sub>  | Chip Disabled (Note 3)                                                                                | 1.8                  |     | 3.6                  | V    |

| Input High Voltage                                          | V <sub>IH</sub>  |                                                                                                       | 0.7V <sub>CC</sub>   |     | V <sub>CC</sub> +0.5 | V    |

| Input Low Voltage                                           | V <sub>IL</sub>  |                                                                                                       | -0.5                 |     | 0.3V <sub>CC</sub>   | V    |

| Output High Voltage                                         | V <sub>OH</sub>  | I <sub>OH</sub> = 0.2mA                                                                               | V <sub>CC</sub> -0.2 |     |                      | V    |

| Output Low Voltage                                          | V <sub>OL</sub>  | I <sub>OL</sub> = -0.2mA                                                                              |                      |     | 0.2                  | V    |

| Input Leakage Current                                       | I <sub>LI</sub>  | $V_{IN} = 0$ to $V_{CC}$                                                                              |                      |     | 0.5                  | μA   |

| Output Leakage Current                                      | I <sub>LO</sub>  | $\overline{OE} = V_{IH}$ or Chip Disabled                                                             |                      |     | 0.5                  | μA   |

| Read/Write Operating Supply Current @ 1 $\mu$ S Cycle Time  | I <sub>CC1</sub> | VCC=3.6 V, $V_{IN}=V_{IH}$ or $V_{IL}$<br>Chip Enabled, IOL = 0                                       |                      |     | 3.0                  | mA   |

| Read/Write Operating Supply Cur-<br>rent @ 70 nS Cycle Time | I <sub>CC2</sub> | VCC=3.6 V, $V_{IN}=V_{IH}$ or $V_{IL}$<br>Chip Enabled, IOL = 0                                       |                      |     | 14.0                 | mA   |

| Read/Write Quiescent Operating<br>Supply Current (Note 1)   | I <sub>CC3</sub> | $V_{IN} = V_{CC} \text{ or } 0V$<br>Chip Enabled, IOL = 0 f = 0,<br>$t_A = 85^{\circ}C$ , VCC = 3.3 V |                      |     | 20                   | μA   |

| Operating Standby Current<br>(Note 1)                       | I <sub>SB1</sub> | $V_{IN} = V_{CC} \text{ or } 0V$<br>Chip Disabled<br>$t_A = 55^{\circ}C, VCC = 3.3V$                  |                      |     | 10                   | μΑ   |

| Maximum Standby Current<br>(Note 1)                         | I <sub>SB2</sub> | $V_{IN} = V_{CC}$ or 0V<br>Chip Disabled<br>$t_A = 85^{\circ}C$ , VCC = 3.3V                          |                      |     | 20                   | μΑ   |

| Maximum Data Retention Current<br>(Note 1)                  | I <sub>DR</sub>  | Vcc = 2.0V, $V_{IN} = V_{CC}$ or 0<br>Chip Disabled, $t_A = 85^{\circ}C$                              |                      |     | 10                   | μΑ   |

Note 1. This device assumes a standby mode if either  $\overline{CE1}$  is disabled (high) or CE2 is disabled (low). It will <u>also</u> automatically go into a standby mode whenever all input signals are quiescent (not toggling) regardless of the state of CE1 or CE2. In order to achieve low standby current in the enabled mode (CE1 low and CE2 high), all inputs must be within 0.2 volts of either  $V_{CC}$  or  $V_{SS}$ .

# TABLE 5: Timing Test Conditions

| Item                                     |                                           |

|------------------------------------------|-------------------------------------------|

| Input Pulse Level                        | 0.1V <sub>CC</sub> to 0.9 V <sub>CC</sub> |

| Input Rise and Fall Time                 | 5ns                                       |

| Input and Output Timing Reference Levels | 0.5 V <sub>CC</sub>                       |

| Output Load                              | CL = 30pF                                 |

| Operating Temperature                    | -40 to +85 °C                             |

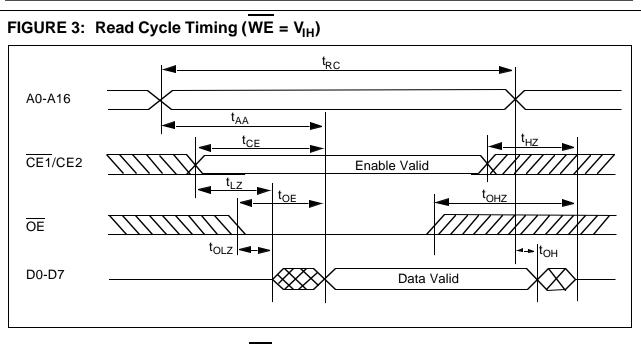

# TABLE 6: Timing

| lion                            | Symbol           | 2.3 - | 3.6 V | 3.0 - | 3.6 V | Units |

|---------------------------------|------------------|-------|-------|-------|-------|-------|

| Item                            |                  | Min.  | Max.  | Min.  | Max.  | Units |

| Read Cycle Time                 | t <sub>RC</sub>  | 70    |       | 55    |       | ns    |

| Address Access Time             | t <sub>AA</sub>  |       | 70    |       | 55    | ns    |

| Chip Enable to Valid Output     | t <sub>co</sub>  |       | 70    |       | 55    | ns    |

| Output Enable to Valid Output   | t <sub>OE</sub>  |       | 25    |       | 20    | ns    |

| Chip Enable to Low-Z output     | t <sub>LZ</sub>  | 10    |       | 10    |       | ns    |

| Output Enable to Low-Z Output   | t <sub>OLZ</sub> | 5     |       | 5     |       | ns    |

| Chip Disable to High-Z Output   | t <sub>HZ</sub>  | 0     | 20    | 0     | 15    | ns    |

| Output Disable to High-Z Output | t <sub>OHZ</sub> | 0     | 20    | 0     | 15    | ns    |

| Output Hold from Address Change | t <sub>OH</sub>  | 10    |       | 10    |       | ns    |

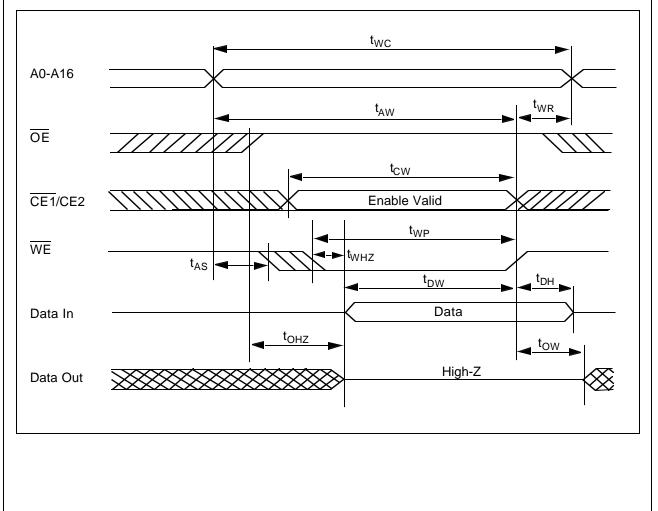

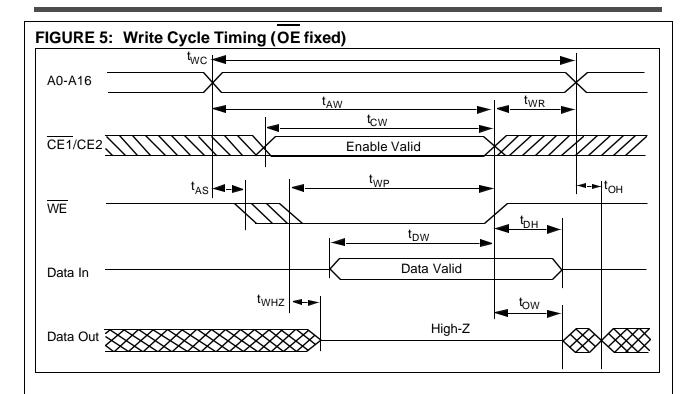

| Write Cycle Time                | t <sub>WC</sub>  | 70    |       | 55    |       | ns    |

| Chip Enable to End of Write     | t <sub>CW</sub>  | 50    |       | 45    |       | ns    |

| Address Valid to End of Write   | t <sub>AW</sub>  | 50    |       | 45    |       | ns    |

| Write Pulse Width               | t <sub>WP</sub>  | 40    |       | 35    |       | ns    |

| Address Setup Time              | t <sub>AS</sub>  | 0     |       | 0     |       | ns    |

| Write Recovery Time             | t <sub>WR</sub>  | 0     |       | 0     |       | ns    |

| Write to High-Z Output          | t <sub>WHZ</sub> | 1     | 20    |       | 15    | ns    |

| Data to Write Time Overlap      | t <sub>DW</sub>  | 40    |       | 35    |       | ns    |

| Data Hold from Write Time       | t <sub>DH</sub>  | 0     |       | 0     |       | ns    |

| End Write to Low-Z Output       | t <sub>OW</sub>  | 5     |       | 5     |       | ns    |

FIGURE 4: Write Cycle Timing (OE clock)

# TABLE 7: Ordering Information

| Part Number | Package      | Package Temperature Voltage<br>Range Range |              | Speed         |

|-------------|--------------|--------------------------------------------|--------------|---------------|

| EM128L08T   | 32 pin TSOP  | -40 to +85°C                               | 2.3 to 3.6 V | 55 ns @ 3.0 V |

| EM128L08N   | 32 pin STSOP | -40 to +85°C                               | 2.3 to 3.6 V | 55 ns @ 3.0 V |

### **TABLE 8: Revision History**

| Revision # | Date      | Change Description      |

|------------|-----------|-------------------------|

| А          | Jan. 2001 | Initial Advance Release |