#### **General Description**

The MAX4321 operational amplifier (op amp) combines a 5MHz gain-bandwidth product and excellent DC accuracy with Rail-to-Rail® operation at both the inputs and the output. This device requires only 650µA and operates from either a single +2.4V to +6.5V supply or dual ±1.2V to ±3.25V supplies, although the MAX4321 typically operates down to +1.8V ( $\pm 0.9V$ ). The MAX4321 remains unity-gain stable with capacitive loads up to 500pF and is capable of driving  $250\Omega$  loads to within 200mV of either rail.

With rail-to-rail input common-mode range and output swing, the MAX4321 is ideal for low-voltage, single-supply applications. In addition, low ±1.2mV input offset voltage and high 2V/µs slew rate make this device ideal for signal-conditioning stages for precision, low-voltage dataacquisition systems. The MAX4321 comes in a spacesaving 5-pin SOT23 package and is guaranteed over the extended (-40°C to +85°C) temperature range.

The MAX4321 is a low-voltage, pin-for-pin compatible upgrade for the LMC7101 that offers five-times higher bandwidth, two-times faster slew rate, and about half the input voltage noise density.

### **Applications**

Battery-Powered Instruments Portable Equipment **Data-Acquisition Systems** Sensor and Signal Conditioning Low-Power, Low-Voltage Applications General-Purpose Low-Voltage Applications

#### **Features**

- ♦ Low-Voltage, Pin-for-Pin Upgrade for LMC7101

- ♦ Guaranteed +2.4V to +6.5V Single-Supply Operation

- ◆ Typically Operates Down to +1.8V

- ♦ 5MHz Gain-Bandwidth Product

- ♦ 650µA Quiescent Current

- ♦ Rail-to-Rail Common-Mode Input Voltage Range

- ♦ Rail-to-Rail Output Voltage Range

- ♦ Drives 250Ω Loads

- ♦ Unity-Gain Stable for Capacitive Loads up to 500pF

- ♦ No Phase Reversal for Overdriven Inputs

- **♦** Low-Cost Solution in SOT23-5 Package

#### **Ordering Information**

| PART         | TEMP.          | PIN-      | TOP  |

|--------------|----------------|-----------|------|

|              | RANGE          | PACKAGE   | MARK |

| MAX4321EUK-T | -40°C to +85°C | 5 SOT23-5 | ADOA |

### Typical Operating Circuit

### SHDN $V_{DD}$ MAXIM DOUT AIN SERIAL INTERFACE VREF CS GND

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

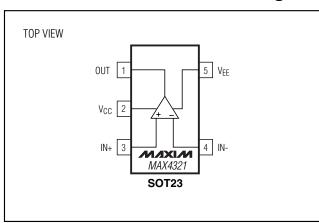

### Pin Configuration/ Functional Diagram

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>CC</sub> to V <sub>EE</sub> )0.3V to +7V All Other Pins(VEE - 0.3V) to (V <sub>CC</sub> + 0.3V) Output Short-Circuit Duration | Operating Temperature Range  Junction Temperature  Storage Temperature Range | +150°C |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------|

| (short to either supply) Continuous Power Dissipation 5-pin SOT23 (derate 7.1mW/°C above +70°C)571mW                                                 | Lead Temperature (soldering, 10s)                                            |        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +5.0V, V_{EE} = 0, V_{CM} = 0, V_{OUT} = V_{CC}/2, R_L = \infty$  connected to  $V_{CC}/2, T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                          | SYMBOL                            | CONDITIONS                                              |                                   | MIN | TYP  | MAX  | UNITS |

|------------------------------------|-----------------------------------|---------------------------------------------------------|-----------------------------------|-----|------|------|-------|

| Supply Voltage Range               | V <sub>CC</sub> - V <sub>EE</sub> |                                                         |                                   | 2.4 |      | 6.5  | V     |

| Supply Current                     |                                   | V <sub>CM</sub> = V <sub>OUT</sub> = V <sub>CC</sub> /2 | $V_{CC} = +2.4V$                  |     | 650  |      | μА    |

|                                    |                                   |                                                         | $V_{CC} = +6.5V$                  |     | 725  |      |       |

| Input Offset Voltage               | Vos                               | V <sub>CM</sub> = V <sub>EE</sub> or V <sub>CC</sub>    |                                   |     | ±1.2 | ±3.5 | mV    |

| Input Bias Current                 | I <sub>BIAS</sub>                 | V <sub>CM</sub> = V <sub>EE</sub> or V <sub>CC</sub>    |                                   |     | ±50  | ±150 | nA    |

| Input Offset Current               | IOFFSET                           | $V_{CM} = V_{EE} \text{ or } V_{CC}$                    |                                   |     | ±4   | ±25  | nA    |

| Differential Input<br>Resistance   | R <sub>IN</sub>                   | -1.5V < V <sub>DIFF</sub> <+1.5V                        |                                   |     | 500  |      | kΩ    |

| Common-Mode Input Voltage<br>Range | V <sub>СМ</sub>                   | Inferred from CMRR test                                 |                                   | VEE |      | Vcc  | V     |

| Common-Mode Rejection<br>Ratio     | CMRR                              | VEE ≤ V <sub>CM</sub> ≤ V <sub>CC</sub>                 |                                   | 60  | 91   |      | dB    |

| Power-Supply Rejection Ratio       | PSRR                              | 2.4V < V <sub>CC</sub> < 6.5V                           |                                   | 66  | 100  |      | dB    |

| Output Resistance                  | Rout                              | $A_V = +1V/V$                                           |                                   |     | 0.1  |      | Ω     |

| Large-Signal Voltage Gain          | Av                                | $V_{OUT} = 0.25V \text{ to } 4.75V, R_L = 100k\Omega$   |                                   |     | 103  |      |       |

|                                    |                                   | $V_{OUT} = 0.40V \text{ to } 4.60V, R_L = 600\Omega$    |                                   |     | 100  |      | dB    |

|                                    |                                   | $V_{OUT} = 0.40V$ to $4.60V$ , $R_L = 250\Omega$        |                                   | 70  | 86   |      |       |

|                                    |                                   | $R_L = 100k\Omega$                                      | V <sub>CC</sub> - V <sub>OH</sub> |     | 25   |      |       |

| Output Voltage Swing               |                                   |                                                         | V <sub>OL</sub> - V <sub>EE</sub> |     | 20   |      | mV    |

|                                    | Vout                              | $R_L = 600\Omega$                                       | V <sub>CC</sub> - V <sub>OH</sub> |     | 135  |      |       |

|                                    | V001                              | nL = 00022                                              | V <sub>OL</sub> - V <sub>EE</sub> |     | 60   |      |       |

|                                    |                                   | $R_L = 250\Omega$                                       | Vcc - Voh                         |     | 200  | 300  |       |

|                                    |                                   | 116 - 20022                                             | V <sub>OL</sub> - V <sub>EE</sub> |     | 100  | 200  |       |

| Output Short-Circuit Current       |                                   |                                                         |                                   |     | 50   |      | mA    |

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +5.0V, V_{EE} = 0, V_{CM} = 0, V_{OUT} = V_{CC}/2, R_L = \infty \ connected \ to \ V_{CC}/2, \textbf{T_A} = -40^{\circ}\textbf{C} \ \textbf{to} \ +85^{\circ}\textbf{C}, \ unless \ otherwise \ noted.) \ (Note \ 1)$

| PARAMETER                                       | SYMBOL                            | CONDITIONS                                           |           | MIN | TYP | MAX  | UNITS |  |

|-------------------------------------------------|-----------------------------------|------------------------------------------------------|-----------|-----|-----|------|-------|--|

| Supply Voltage Range                            | V <sub>CC</sub> - V <sub>EE</sub> |                                                      |           | 2.4 |     | 6.5  | V     |  |

| Supply Current                                  | Icc                               | $V_{CM} = V_{OUT} = V_{CC}/2$                        |           |     |     | 1200 | μА    |  |

| Input Offset Voltage                            | Vos                               | V <sub>CM</sub> = V <sub>EE</sub> or V <sub>CC</sub> |           |     |     | ±6   | mV    |  |

| Input Offset Voltage<br>Temperature Coefficient |                                   |                                                      |           |     | ±2  |      | μV/°C |  |

| Input Bias Current                              | I <sub>BIAS</sub>                 | V <sub>CM</sub> = V <sub>EE</sub> or V <sub>CC</sub> |           |     |     | ±180 | nA    |  |

| Input Offset Current                            | IOFFSET                           | V <sub>CM</sub> = V <sub>EE</sub> or V <sub>CC</sub> |           |     |     | ±50  | nA    |  |

| Common-Mode Input Voltage<br>Range              | V <sub>CM</sub>                   | Inferred from CMRR test                              |           | VEE |     | Vcc  | ٧     |  |

| Common-Mode Rejection Ratio                     | CMRR                              | V <sub>EE</sub> ≤ V <sub>CM</sub> ≤ V <sub>CC</sub>  |           | 54  |     |      | dB    |  |

| Power-Supply Rejection Ratio                    | PSRR                              | 2.4V < V <sub>CC</sub> < 6.5V                        |           | 62  |     |      | dB    |  |

| Large-Signal Voltage Gain                       | Ay                                | $V_{OUT}$ = 0.40V to 4.60V, $R_L$ = 250 $\Omega$     |           | 66  |     |      | dB    |  |

| Output Voltage Swing                            | V <sub>OUT</sub>                  | $R = 250\Omega$                                      | VCC - VOH |     |     | 350  | mV    |  |

|                                                 | .001                              | V <sub>OL</sub> - V <sub>EE</sub>                    |           |     |     | 250  |       |  |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5.0V, V_{EE} = 0, V_{CM} = 0, V_{OUT} = V_{CC}/2, R_L = 250\Omega$  connected to  $V_{CC}/2, T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                           | SYMBOL  | CONDITIONS                                      | MIN TYP MAX | UNITS   |

|-------------------------------------|---------|-------------------------------------------------|-------------|---------|

| Gain-Bandwidth Product              | GBP     |                                                 | 5           | MHz     |

| Phase Margin                        |         |                                                 | 64          | degrees |

| Gain Margin                         |         |                                                 | 12          | dB      |

| Total Harmonic Distortion and Noise | THD+N   | 10kHz tone, $V_{OUT} = 2Vpp$ ,<br>$A_V = +1V/V$ | 0.003       | %       |

| Slew Rate                           | SR      | V <sub>OUT</sub> = 1V step                      | 2           | V/µs    |

| Settling Time to 0.01%              | tSETTLE | $V_{OUT} = 2V$ step, $A_V = +1V/V$              | 2           | μs      |

| Turn-On Time                        | ton     | V <sub>CC</sub> = 0 to 3V step                  | 1           | μs      |

| Input Capacitance                   | CIN     |                                                 | 3           | рF      |

| Input Noise Voltage Density         |         | f = 1kHz                                        | 22          | nV/√ Hz |

| Input Noise Current Density         |         | f = 1kHz                                        | 0.4         | pA/√Hz  |

Note 1: All devices are 100% production tested at  $T_A = +25^{\circ}C$ . All temperature limits are guaranteed by design and characterization.

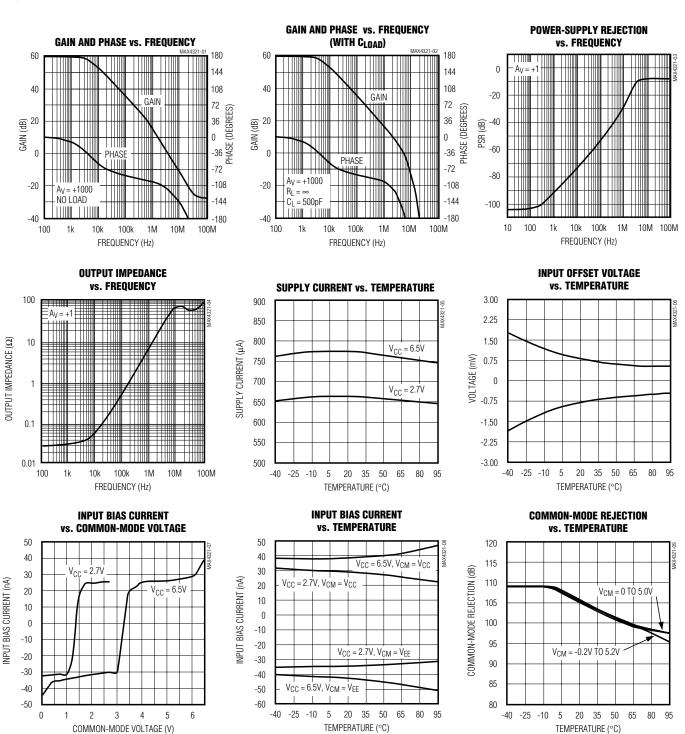

### **Typical Operating Characteristics**

$(VCC = +5V, VEE = 0, VCM = VCC/2, TA = +25^{\circ}C, unless otherwise noted.)$

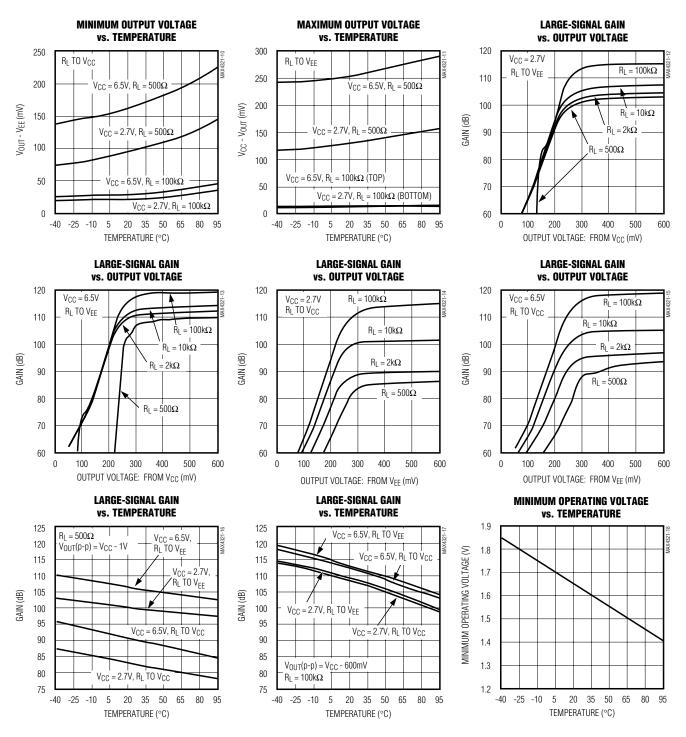

### **Typical Operating Characteristics (continued)**

$(VCC = +5V, VEE = 0, VCM = VCC/2, TA = +25^{\circ}C, unless otherwise noted.)$

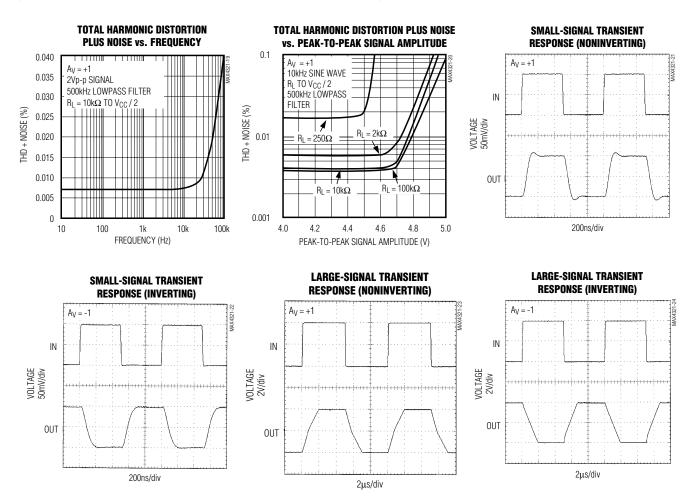

### Typical Operating Characteristics (continued)

$(VCC = +5V, VEE = 0, VCM = VCC/2, TA = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN | NAME | FUNCTION                                                        |

|-----|------|-----------------------------------------------------------------|

| 1   | OUT  | Output                                                          |

| 2   | Vcc  | Positive Supply                                                 |

| 3   | IN+  | Noninverting Input                                              |

| 4   | IN-  | Inverting Input                                                 |

| 5   | VEE  | Negative Supply. Connect to ground for single-supply operation. |

### Applications Information

Rail-to-Rail Input Stage

The MAX4321 high-speed amplifier has rail-to-rail input and output stages designed for low-voltage, single-supply operation. The input stage consists of separate NPN and PNP differential stages, which combine to provide an input common-mode range extending to the supply rails. The PNP stage is active for input voltages close to the negative rail, and the NPN stage is active for input voltages near the positive rail. The switchover transition region, which occurs near VCC / 2, has been extended to minimize the slight degradation in CMRR caused by the mismatch of the input pairs. Its low offset voltage, high bandwidth, and rail-to-rail common-mode range makes this op amp an excellent choice for precision, low-voltage, data-acquisition systems.

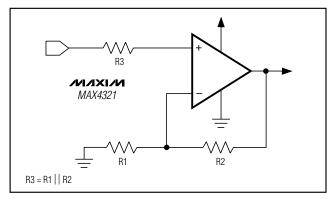

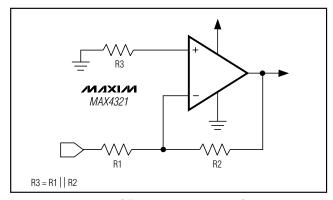

Since the input stage switches between the NPN and PNP pairs, the input bias current changes polarity as the input voltage passes through the transition region. To reduce the offset error caused by input bias cur-

rents flowing through external source impedances, match the effective impedance seen by each input (Figures 1a, 1b). High source impedances, together with the input capacitance, can create a parasitic pole that produces an underdamped signal response. Reducing the input impedance or placing a small (2pF to 10pF) capacitor across the feedback resistor improves the response.

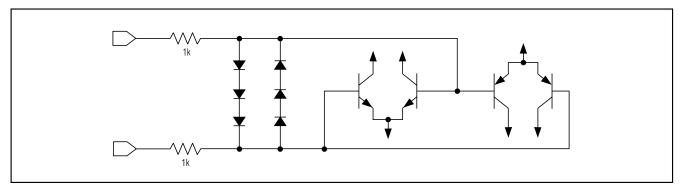

The MAX4321's inputs are protected from large differential input voltages by  $1k\Omega$  series resistors and back-to-back triple diodes across the inputs (Figure 2). For differential input voltages less than 1.8V, the input resistance is typically  $500k\Omega$ . For differential input voltages greater than 1.8V, the input resistance is approximately  $2k\Omega$ , and the input bias current is determined by the following equation:

$$I_{BIAS} = \frac{V_{DIFF} - 1.8V}{2k\Omega}$$

Figure 1a. Reducing Offset Error Due to Bias Current (Noninverting)

Figure 1b. Reducing Offset Error Due to Bias Current (Inverting)

Figure 2. Input Protection Circuit

#### Rail-to-Rail Output Stage

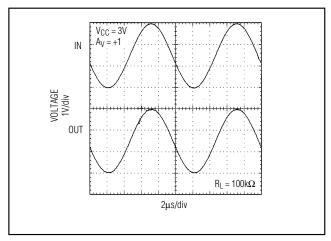

The minimum output voltage will be within millivolts of ground for single-supply operation where the load is referenced to ground (VEE). Figure 3 shows the input voltage range and output voltage swing of a MAX4321 connected as a voltage follower. With a +3V supply and the 100k $\Omega$  load tied to ground, the output swings from 0.02V to 2.97V. The maximum output voltage swing depends on the load but will be within 300mV of a +5V supply, even with the maximum load (250 $\Omega$  to ground).

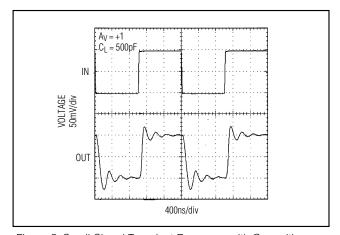

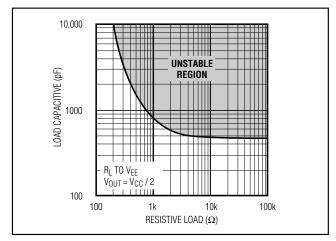

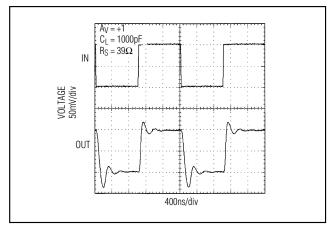

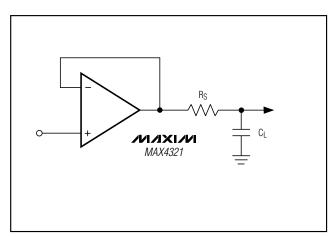

Driving a capacitive load can cause instability in most high-speed op amps, especially those with low quiescent current. The MAX4321 has a high tolerance for capacitive loads. It is stable with capacitive loads up to 500pF. Figure 4 gives the stable operating region for capacitive loads. Figures 5 and 6 show the response with capacitive loads and the results of adding an isolation resistor in series with the output (Figure 7). The resistor improves the circuit's phase margin by isolating the load capacitor from the op amp's output.

Figure 3. Rail-to-Rail Input /Output Voltage Range

Figure 5. Small-Signal Transient Response with Capacitive Load

Figure 4. Capacitive-Load Stability

Figure 6. Transient Response to Capacitive Load with Isolation Resistor

#### Power-Up

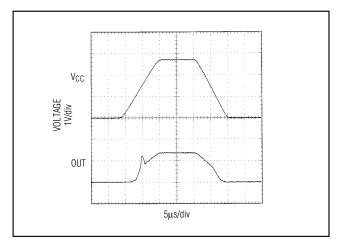

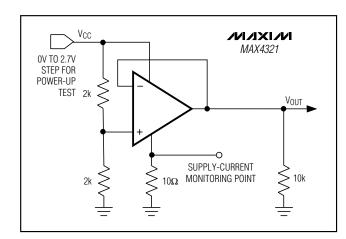

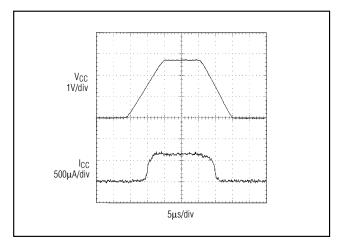

The MAX4321 typically settles within 1µs after power-up. Using the test circuit of Figure 8, Figures 9 and 10 show the output voltage and supply current on power-up.

#### **Power Supplies and Layout**

The MAX4321 operates from single +2.4V to +6.5V or dual  $\pm 1.2$ V to  $\pm 3.25$ V supplies, though it typically operates down to +1.8V ( $\pm 0.9$ V). For single-supply operation, bypass the power supply with a 0.1 $\mu$ F ceramic capacitor in parallel with at least 1 $\mu$ F. For dual supplies, bypass each supply to ground.

Good layout improves performance by decreasing the amount of stray capacitance at the op amp's inputs and outputs. To decrease stray capacitance, minimize trace lengths and resistor leads by placing external components close to the op amp's pins.

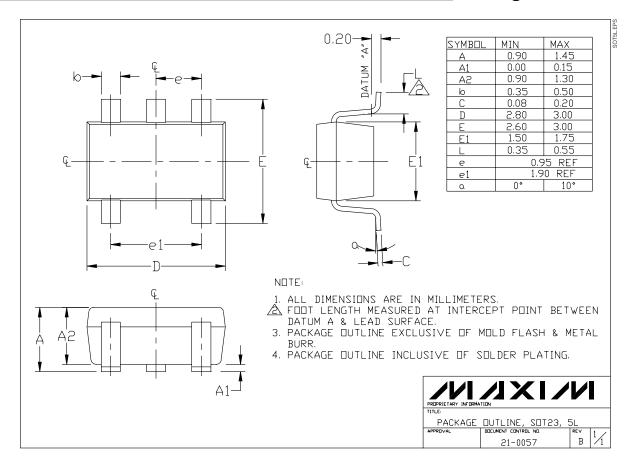

#### Package Information

TRANSISTOR COUNT: 84

Figure 7. Capacitive-Load-Driving Circuit

Figure 9. Power-Up Output Voltage

Figure 8. Power-Up Test Circuit

Figure 10. Power-Up Supply Current

### **Package Information**

0 \_\_\_\_\_\_ NIXI/N

# MAX4321

# Low-Cost, Low-Voltage, Rail-to-Rail, Input/Output, SOT23 5MHz Op Amp

**NOTES**

**MAXIM** \_\_\_\_\_\_\_ 11

**NOTES**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.