# LPV321-N Single/LPV358 Dual/LPV324 Quad General Purpose, Low Voltage, Low Power, Rail-to-Rail Output Operational Amplifiers

Check for Samples: LPV321, LPV324-N, LPV358-N

#### **FEATURES**

(For  $V^+ = 5V$  and  $V^- = 0V$ , Typical Unless Otherwise Noted)

- **Ensured 2.7V and 5V Performance**

- **No Crossover Distortion**

- Space Saving Package

- 5-Pin SC70 2.0x2.1x1.0 mm

- Industrial Temperature Range, -40°C to +85°C

- Gain-Bandwidth Product, 152 kHz

- **Low Supply Current**

- LPV321-N, 9 μA

- LPV358, 15 μA

- LPV324, 28 μA

- Rail-to-Rail Output Swing @ 100 kΩ Load

- V⁺-3.5 mV

- V<sup>-</sup>+90 mV

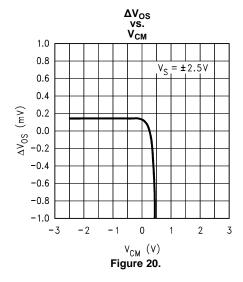

- $V_{CM}$ , -0.2V to V<sup>+</sup>-0.8V

#### **APPLICATIONS**

- **Active Filters**

- **General Purpose Low Voltage Applications**

- **General Purpose Portable Devices**

#### DESCRIPTION

The LPV321-N/358/324 are low power (9 µA per channel at 5.0V) versions of the LMV321/358/324 op amps. This is another addition to the LMV321-N/358/324 family of commodity op amps.

The LPV321-N/358/324 are the most cost effective solutions for the applications where low voltage, low power operation, space saving and low price are needed. The LPV321-N/358/324 have rail-to-rail output swing capability and the input common-mode voltage range includes ground. They all exhibit excellent speed-power ratio, achieving 5 kHz of bandwidth with a supply current of only 9 µA.

The LPV321-N is available in space saving 5-Pin SC70, which is approximately half the size of 5-Pin SOT-23. The small package saves space on PC boards, and enables the design of small portable electronic devices. It also allows the designer to place the device closer to the signal source to reduce noise pickup and increase signal integrity.

The chips are built with Texas Instruments's advanced submicron silicon-gate BiCMOS process. The LPV321-N/358/324 have bipolar input and output stages for improved noise performance and higher output current drive.

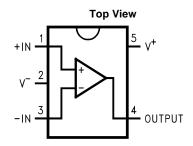

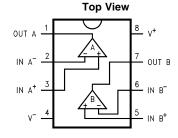

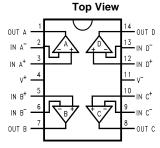

## **Connection Diagram**

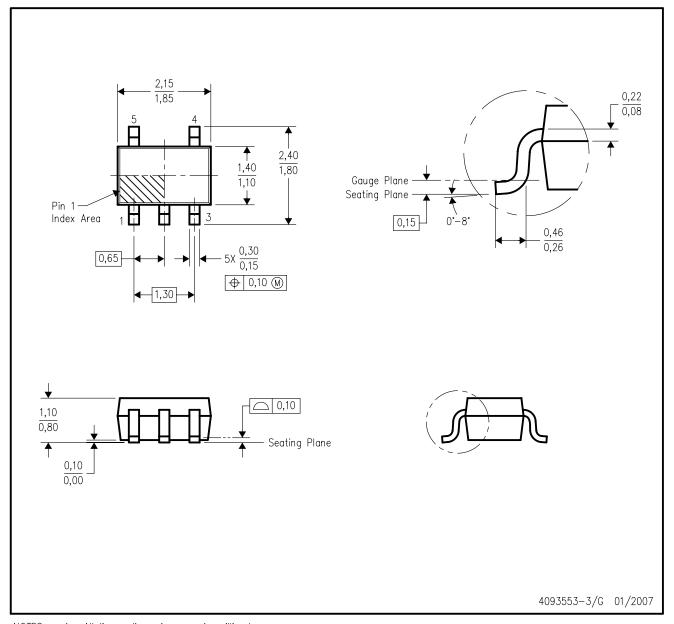

Figure 1. 5-Pin SC70 and SOT-23 **Packages** See Package Numbers DCK0005A and DBV0005A

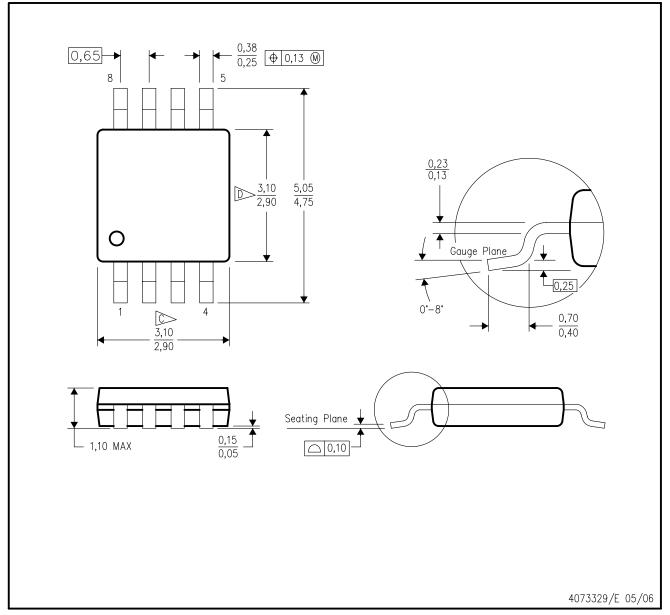

Figure 2. 8-Pin SOIC and VSSOP **Packages** See Package Numbers D0008A and DGK0008A

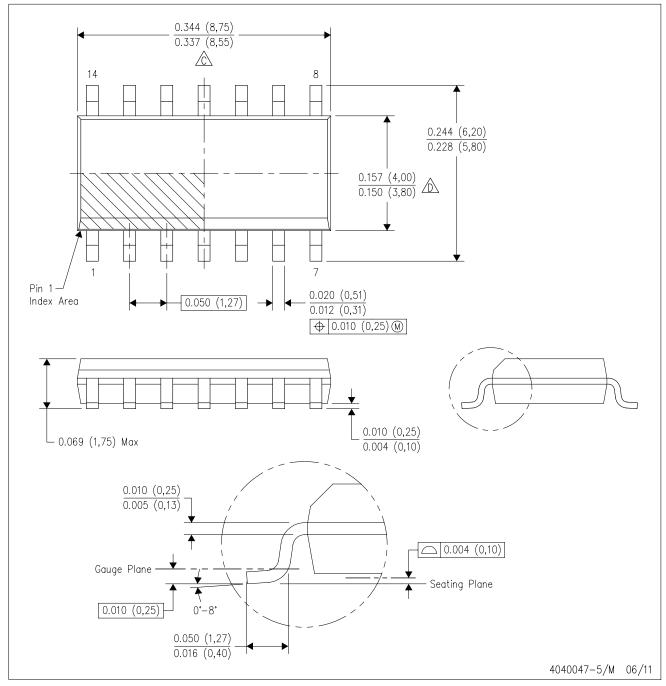

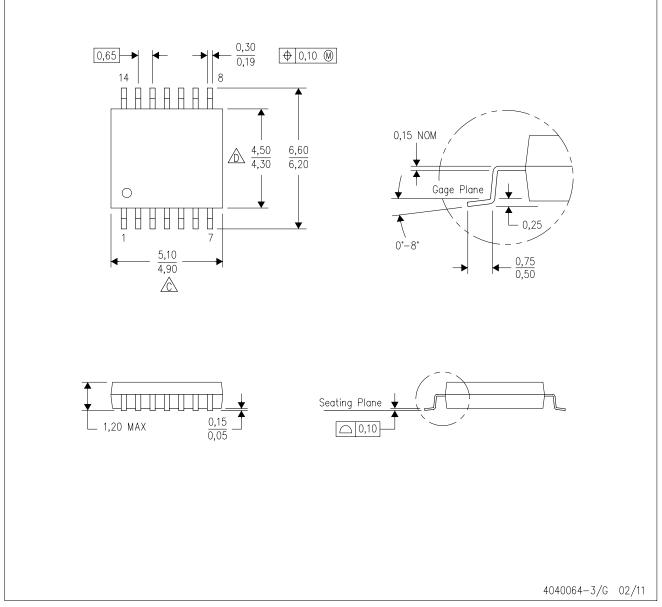

Figure 3. 14-Pin SOIC and TSSOP **Packages** See Package Numbers D0014A and PW0014A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## Absolute Maximum Ratings (1)(2)

| ESD Tolerance (3)                                    |                 |

|------------------------------------------------------|-----------------|

| Human Body Model                                     |                 |

| LPV324                                               | 2000V           |

| LPV358                                               | 1500V           |

| LPV321-N                                             | 1500V           |

| Machine Model                                        | 100V            |

| Differential Input Voltage                           | ±Supply Voltage |

| Supply Voltage (V <sup>+</sup> –V <sup>-</sup> )     | 5.5V            |

| Output Short Circuit to V +                          | (4)             |

| Output Short Circuit to V -                          | (5)             |

| Soldering Information                                |                 |

| Infrared or Convection (20 sec)                      | 235°C           |

| Storage Temperature Range                            | −65°C to 150°C  |

| Junction Temp. (T <sub>J</sub> , max) <sup>(6)</sup> | 150°C           |

- Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

- If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC)Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

- Shorting output to  $V^+$  will adversely affect reliability. Shorting output to  $V^-$  will adversely affect reliability.

- The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

## Operating Ratings (1)

| Supply Voltage                                      | 2.7V to 5V     |

|-----------------------------------------------------|----------------|

| Temperature Range                                   | -40°C to +85°C |

| Thermal Resistance ( $\theta_{JA}$ ) <sup>(2)</sup> |                |

| 5-Pin SC70                                          | 478°C/W        |

| 5-Pin SOT-23                                        | 265°C/W        |

| 8-Pin SOIC                                          | 190°C/W        |

| 8-Pin VSSOP                                         | 235°C/W        |

| 14-Pin SOIC                                         | 145°C/W        |

| 14-Pin TSSOP                                        | 155°C/W        |

|                                                     |                |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

All numbers are typical, and apply for packages soldered directly onto a PC board in still air.

Submit Documentation Feedback

#### 2.7V DC Electrical Characteristics

Unless otherwise specified, all limits specified for  $T_J$  = 25°C,  $V^+$  = 2.7V,  $V^-$  = 0V,  $V_{CM}$  = 1.0V,  $V_O$  =  $V^+/2$  and  $R_L$  > 1  $M\Omega$ .

|                   | Parameter                          | Test Conditions                                       | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units |  |

|-------------------|------------------------------------|-------------------------------------------------------|--------------------|--------------------|--------------------|-------|--|

| Vos               | Input Offset Voltage               |                                                       |                    | 1.2                | 7                  | mV    |  |

| TCV <sub>OS</sub> | Input Offset Voltage Average Drift |                                                       |                    | 2                  |                    | μV/°C |  |

| I <sub>B</sub>    | Input Bias Current                 |                                                       |                    | 1.7                | 50                 | nA    |  |

| Ios               | Input Offset Current               |                                                       |                    | 0.6                | 40                 | nA    |  |

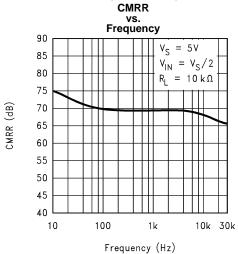

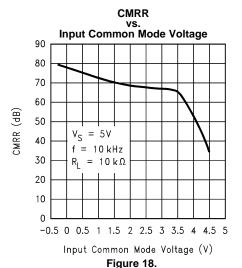

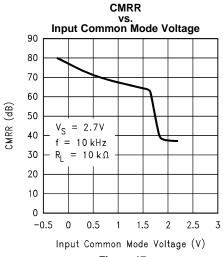

| CMRR              | Common Mode Rejection Ratio        | 0V ≤ V <sub>CM</sub> ≤ 1.7V                           | 50                 | 70                 |                    | dB    |  |

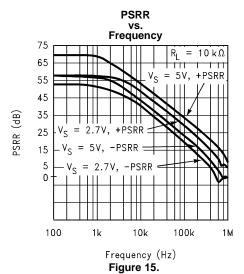

| PSRR              | Power Supply Rejection Ratio       | $2.7V \le V^{+} \le 5V$<br>$V_{O} = 1V, V_{CM} = 1V$  | 50                 | 65                 |                    | dB    |  |

| V <sub>CM</sub>   | Input Common-Mode Voltage<br>Range | For CMRR ≥ 50 dB                                      | 0                  | -0.2               |                    | V     |  |

|                   |                                    |                                                       |                    | 1.9                | 1.7                | V     |  |

| Vo                | Output Swing                       | $R_L = 100 \text{ k}\Omega \text{ to } 1.35 \text{V}$ | V+ -100            | V+ -3              |                    |       |  |

|                   |                                    |                                                       |                    | 80                 | 180                | mV    |  |

| I <sub>S</sub>    | Supply Current                     | LPV321-N                                              |                    | 4                  | 8                  |       |  |

|                   |                                    | LPV358<br>Both Amplifiers                             |                    | 8                  | 16                 | μA    |  |

|                   |                                    | LPV324<br>All Four Amplifiers                         |                    | 16                 | 24                 | 1     |  |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

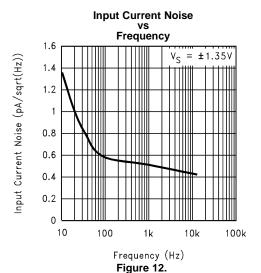

#### 2.7V AC Electrical Characteristics

Unless otherwise specified, all limits specified for  $T_J = 25^{\circ}C$ ,  $V^+ = 2.7V$ ,  $V^- = 0V$ ,  $V_{CM} = 1.0V$ ,  $V_O = V^+/2$  and  $R_L > 1$  M $\Omega$ .

|                | Parameter                    | Test Conditions        | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units              |

|----------------|------------------------------|------------------------|--------------------|--------------------|--------------------|--------------------|

| GBWP           | Gain-Bandwidth Product       | C <sub>L</sub> = 22 pF |                    | 112                |                    | kHz                |

| $\Phi_{m}$     | Phase Margin                 |                        |                    | 97                 |                    | Deg                |

| G <sub>m</sub> | Gain Margin                  |                        |                    | 35                 |                    | dB                 |

| e <sub>n</sub> | Input-Referred Voltage Noise | f = 1 kHz              |                    | 178                |                    | nV/√ <del>Hz</del> |

| in             | Input-Referred Current Noise | f = 1 kHz              |                    | 0.50               |                    | pA/√ <del>Hz</del> |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

## **5V DC Electrical Characteristics**

Unless otherwise specified, all limits specified for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = 2.0V$ ,  $V_O = V^+/2$  and  $R_L > 1$  M $\Omega$ . **Boldface** limits apply at the temperature extremes.

|                   | Parameter                          | Test Conditions        | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units |

|-------------------|------------------------------------|------------------------|--------------------|--------------------|--------------------|-------|

| Vos               | Input Offset Voltage               |                        |                    | 1.5                | 7<br>10            | mV    |

| TCV <sub>OS</sub> | Input Offset Voltage Average Drift |                        |                    | 2                  |                    | μV/°C |

| I <sub>B</sub>    | Input Bias Current                 |                        |                    | 2                  | 50<br><b>60</b>    | nA    |

| I <sub>OS</sub>   | Input Offset Current               |                        |                    | 0.6                | 40<br><b>50</b>    | nA    |

| CMRR              | Common Mode Rejection Ratio        | $0V \le V_{CM} \le 4V$ | 50                 | 71                 |                    | dB    |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

### 5V DC Electrical Characteristics (continued)

Unless otherwise specified, all limits specified for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = 2.0V$ ,  $V_O = V^+/2$  and  $R_L > 1$  M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Parameter       |                                       | Test Conditions                                      | Min <sup>(1)</sup>                         | Typ <sup>(2)</sup>  | Max <sup>(1)</sup> | Units |  |

|-----------------|---------------------------------------|------------------------------------------------------|--------------------------------------------|---------------------|--------------------|-------|--|

| PSRR            | Power Supply Rejection Ratio          | $2.7V \le V^{+} \le 5V$<br>$V_{O} = 1V, V_{CM} = 1V$ | 50                                         | 65                  |                    | dB    |  |

| V <sub>CM</sub> | Input Common-Mode Voltage             | For CMRR ≥ 50 dB                                     | 0                                          | -0.2                |                    | V     |  |

|                 | Range                                 |                                                      |                                            | 4.2                 | 4                  | V     |  |

| A <sub>V</sub>  | Large Signal Voltage Gain             | $R_L = 100 \text{ k}\Omega$                          | 15<br><b>10</b>                            | 100                 |                    | V/mV  |  |

| Vo              | Output Swing                          | $R_L = 100 \text{ k}\Omega \text{ to } 2.5 \text{V}$ | V <sup>+</sup> -100<br>V <sup>+</sup> -200 | V <sup>+</sup> −3.5 |                    | m)/   |  |

|                 |                                       |                                                      |                                            | 90                  | 180<br><b>220</b>  | mV    |  |

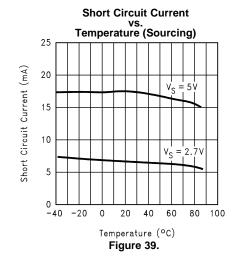

| Io              | Output Short Circuit Current Sourcing | LPV324, LPV358, and LPV321-N<br>V <sub>O</sub> = 0V  | 2                                          | 16                  |                    |       |  |

|                 | Output Short Circuit Current Sinking  | LPV321-N<br>V <sub>O</sub> = 5V                      | 20                                         | 60                  |                    | mA    |  |

|                 |                                       | LPV324 and LPV358<br>V <sub>O</sub> = 5V             | 11                                         | 16                  |                    |       |  |

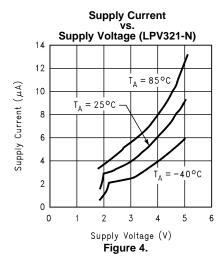

| I <sub>S</sub>  | Supply Current                        | LPV321-N                                             | 9                                          |                     | 12<br><b>15</b>    |       |  |

|                 |                                       | LPV358<br>Both amplifiers                            |                                            | 15                  | 20<br><b>24</b>    | μA    |  |

|                 |                                       | LPV324<br>All four amplifiers                        |                                            | 28 42<br><b>46</b>  |                    |       |  |

<sup>(3)</sup>  $R_L$  is connected to  $V^-$ . The output voltage is  $0.5V \le V_O \le 4.5V$ .

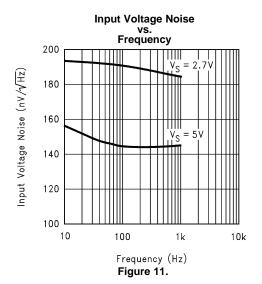

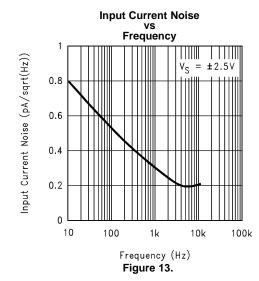

#### **5V AC Electrical Characteristics**

Unless otherwise specified, all limits specified for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = 2.0V$ ,  $V_O = V^+/2$  and  $R_L > 1M\Omega$ . **Boldface** limits apply at the temperature extremes.

|                | Parameter                    | Test Conditions        | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Min <sup>(1)</sup> | Units              |

|----------------|------------------------------|------------------------|--------------------|--------------------|--------------------|--------------------|

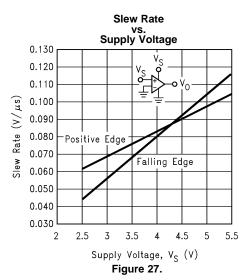

| SR             | Slew Rate                    | (3)                    |                    | 0.1                |                    | V/µs               |

| GBWP           | Gain-Bandwidth Product       | C <sub>L</sub> = 22 pF |                    | 152                |                    | kHz                |

| $\Phi_{m}$     | Phase Margin                 |                        |                    | 87                 |                    | Deg                |

| G <sub>m</sub> | Gain Margin                  |                        |                    | 19                 |                    | dB                 |

| e <sub>n</sub> | Input-Referred Voltage Noise | f = 1  kHz,            |                    | 146                |                    | nV/√ <del>Hz</del> |

| i <sub>n</sub> | Input-Referred Current Noise | f = 1 kHz              |                    | 0.30               |                    | pA/√ <del>Hz</del> |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

Submit Documentation Feedback

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(3)</sup> Connected as voltage follower with 3V step input. Number specified is the slower of the positive and negative slew rates.

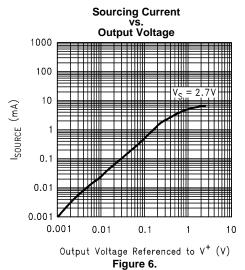

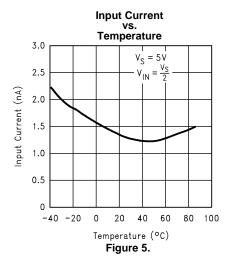

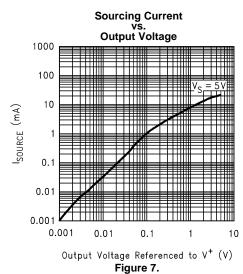

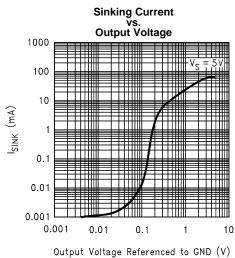

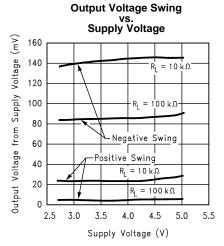

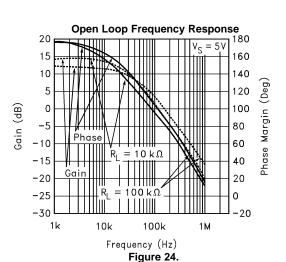

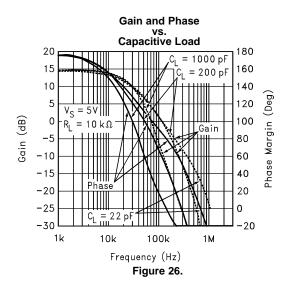

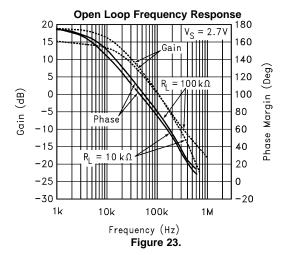

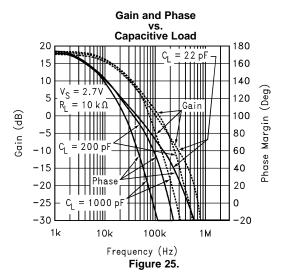

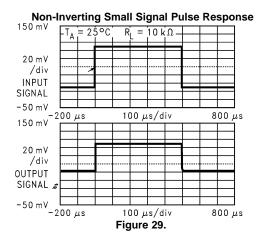

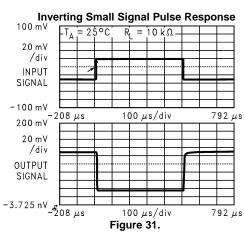

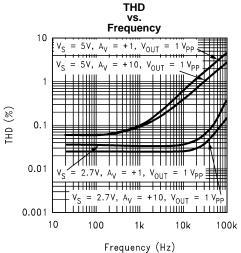

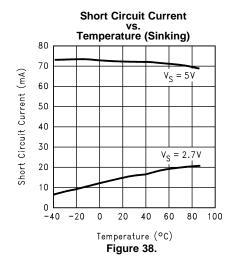

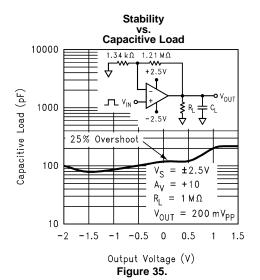

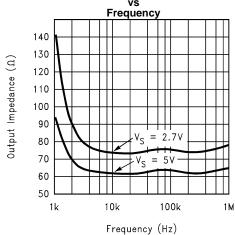

## **Typical Performance Characteristics**

Figure 9.

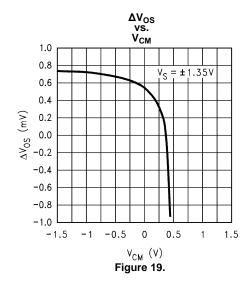

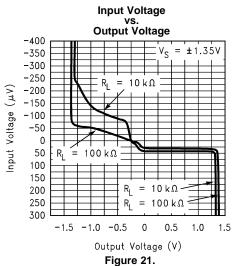

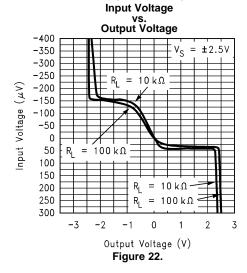

Unless otherwise specified,  $V_S = +5V$ , single supply,  $T_A = 25$ °C.

Figure 10.

**Crosstalk Rejection** vs. Frequency 120  $\mathrm{V}_{\mathrm{S}}$ = 5V 110  $R_{\mathsf{L}}$  $= 100 k\Omega$ 100 Crosstalk Rejection (dB) 90 80 70 60 50 40 30 20 100 10k 1k 100k Frequency (Hz)

Figure 14.

Figure 16.

Figure 17.

Output Voltage (V) Figure 34.

Figure 36.

Open Loop Output Impedance vs

Figure 37.

#### **APPLICATION INFORMATION**

## Benefits of the LPV321-N/358/324

#### Size

The small footprints of the LPV321-N/358/324 packages save space on printed circuit boards, and enable the design of smaller electronic products, such as cellular phones, pagers, or other portable systems. The low profile of the LPV321-N/358/324 make them possible to use in PCMCIA type III cards.

#### Signal Integrity

Signals can pick up noise between the signal source and the amplifier. By using a physically smaller amplifier package, the LPV321-N/358/324 can be placed closer to the signal source, reducing noise pickup and increasing signal integrity.

## **Simplified Board Layout**

These products help you to avoid using long pc traces in your pc board layout. This means that no additional components, such as capacitors and resistors, are needed to filter out the unwanted signals due to the interference between the long pc traces.

### **Low Supply Current**

These devices will help you to maximize battery life. They are ideal for battery powered systems.

#### Low Supply Voltage

TI provides ensured performance at 2.7V and 5V. These specifications ensure operation throughout the battery lifetime.

#### Rail-to-Rail Output

Rail-to-rail output swing provides maximum possible dynamic range at the output. This is particularly important when operating on low supply voltages.

#### **Input Includes Ground**

Allows direct sensing near GND in single supply operation.

The differential input voltage may be larger than V<sup>+</sup> without damaging the device. Protection should be provided to prevent the input voltages from going negative more than −0.3V (at 25°C). An input clamp diode with a resistor to the IC input terminal can be used.

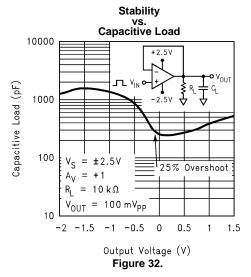

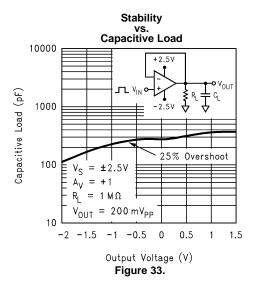

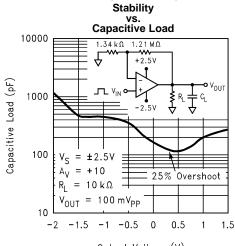

#### **Capacitive Load Tolerance**

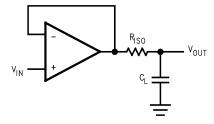

The LPV321-N/358/324 can directly drive 200 pF in unity-gain without oscillation. The unity-gain follower is the most sensitive configuration to capacitive loading. Direct capacitive loading reduces the phase margin of amplifiers. The combination of the amplifier's output impedance and the capacitive load induces phase lag. This results in either an underdamped pulse response or oscillation. To drive a heavier capacitive load, circuit in Figure 40 can be used.

Figure 40. Indirectly Driving A Capacitive Load Using Resistive Isolation

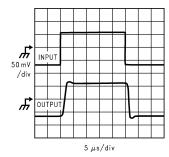

In Figure 40, the isolation resistor  $R_{ISO}$  and the load capacitor  $C_L$  form a pole to increase stability by adding more phase margin to the overall system. The desired performance depends on the value of  $R_{ISO}$ . The bigger the  $R_{ISO}$  resistor value, the more stable  $V_{OUT}$  will be. Figure 41 is an output waveform of Figure 40 using 100 k $\Omega$  for  $R_{ISO}$  and 1000 pF for  $C_I$ .

Figure 41. Pulse Response of the LPV324 Circuit in Figure 40

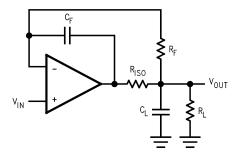

The circuit in Figure 42 is an improvement to the one in Figure 40 because it provides DC accuracy as well as AC stability. If there were a load resistor in Figure 40, the output would be voltage divided by  $R_{\rm ISO}$  and the load resistor. Instead, in Figure 42,  $R_{\rm F}$  provides the DC accuracy by using feed-forward techniques to connect  $V_{\rm IN}$  to  $R_{\rm L}$ . Caution is needed in choosing the value of  $R_{\rm F}$  due to the input bias current of the LPV321-N/358/324.  $C_{\rm F}$  and  $R_{\rm ISO}$  serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier's inverting input, thereby preserving phase margin in the overall feedback loop. Increased capacitive drive is possible by increasing the value of  $C_{\rm F}$ . This in turn will slow down the pulse response.

Figure 42. Indirectly Driving A Capacitive Load with DC Accuracy

#### **Input Bias Current Cancellation**

The LPV321-N/358/324 family has a bipolar input stage. The typical input bias current of LPV321-N/358/324 is 1.5 nA with 5V supply. Thus a 100 k $\Omega$  input resistor will cause 0.15 mV of error voltage. By balancing the resistor values at both inverting and non-inverting inputs, the error caused by the amplifier's input bias current will be reduced. The circuit in Figure 43 shows how to cancel the error caused by input bias current.

Figure 43. Cancelling the Error Caused by Input Bias Current

Submit Documentation Feedback

### **Typical Single-Supply Application Circuits**

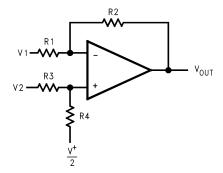

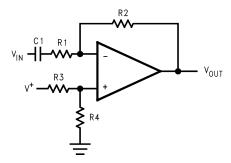

### **Difference Amplifier**

The difference amplifier allows the subtraction of two voltages or, as a special case, the cancellation of a signal common to two inputs. It is useful as a computational amplifier, in making a differential to single-ended conversion or in rejecting a common mode signal.

Figure 44. Difference Amplifier

$$V_{OUT} = \left(\frac{R1 + R2}{R3 + R4}\right) \frac{R4}{R1} V_2 - \frac{R2}{R1} V_1 + \left(\frac{R1 + R2}{R3 + R4}\right) \frac{R3}{R1} \cdot \frac{V^+}{2}$$

for R1 = R3 and R2 = R4

$$V_{OUT} = \frac{R2}{R1} \left(V_2 - V_1\right) + \frac{V^+}{2}$$

(1)

#### Instrumentation Circuits

The input impedance of the previous difference amplifier is set by the resistor  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ . To eliminate the problems of low input impedance, one way is to use a voltage follower ahead of each input as shown in the following two instrumentation amplifiers.

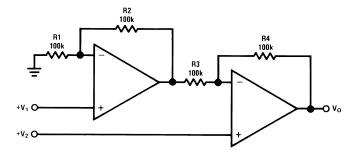

#### Three-op-amp Instrumentation Amplifier

The quad LPV324 can be used to build a three-op-amp instrumentation amplifier as shown in Figure 45

Figure 45. Three-op-amp Instrumentation Amplifier

The first stage of this instrumentation amplifier is a differential-input, differential-output amplifier, with two voltage followers. These two voltage followers assure that the input impedance is over 100 M $\Omega$ . The gain of this instrumentation amplifier is set by the ratio of  $R_2/R_1$ .  $R_3$  should equal  $R_1$  and  $R_4$  equal  $R_2$ . Matching of  $R_3$  to  $R_1$  and  $R_4$  to  $R_2$  affects the CMRR. For good CMRR over temperature, low drift resistors should be used. Making  $R_4$  Slightly smaller than  $R_2$  and adding a trim pot equal to twice the difference between  $R_2$  and  $R_4$  will allow the CMRR to be adjusted for optimum.

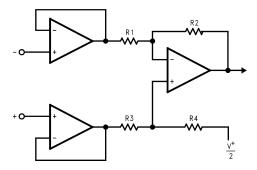

#### Two-op-amp Instrumentation Amplifier

A two-op-amp instrumentation amplifier can also be used to make a high-input-impedance DC differential amplifier (Figure 46). As in the three-op-amp circuit, this instrumentation amplifier requires precise resistor matching for good CMRR.  $R_4$  should equal to  $R_1$  and  $R_3$  should equal  $R_2$ .

Figure 46. Two-op-amp Instrumentation Amplifier

$$V_0 = \left(1 + \frac{R4}{R3}\right)(V_2 - V_1)$$

, where R1 = R4 and R2 = R3

As shown:  $V_0 = 2(V_2 - V_1)$

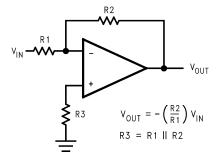

### Single-Supply Inverting Amplifier

There may be cases where the input signal going into the amplifier is negative. Because the amplifier is operating in single supply voltage, a voltage divider using  $R_3$  and  $R_4$  is implemented to bias the amplifier so the input signal is within the input common-common voltage range of the amplifier. The capacitor  $C_1$  is placed between the inverting input and resistor  $R_1$  to block the DC signal going into the AC signal source,  $V_{IN}$ . The values of  $R_1$  and  $C_1$  affect the cutoff frequency,

$$fc = 1/2\pi R_1 C_1$$

(3)

As a result, the output signal is centered around mid-supply (if the voltage divider provides  $V^+/2$  at the non-inverting input). The output can swing to both rails, maximizing the signal-to-noise ratio in a low voltage system.

Figure 47. Single-Supply Inverting Amplifier

$$V_{OUT} = -\frac{R2}{R1} V_{IN}$$

(4)

#### **Active Filter**

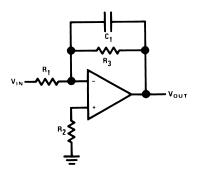

#### Simple Low-Pass Active Filter

The simple low-pass filter is shown in Figure 48. Its low-frequency gain( $\omega \to 0$ ) is defined by  $-R_3/R_1$ . This allows low-frequency gains other than unity to be obtained. The filter has a -20 dB/decade roll-off after its corner frequency fc.  $R_2$  should be chosen equal to the parallel combination of  $R_1$  and  $R_3$  to minimize errors due to bais current. The frequency response of the filter is shown in Figure 49

Submit Documentation Feedback

Figure 48. Simple Low-Pass Active Filter

$$A_{L} = -\frac{R_{3}}{R_{1}}$$

$$f_{c} = \frac{1}{2\pi R_{3} C_{1}}$$

$$R_{2} = R_{1} || R_{3}$$

$$f_{c} = \frac{1}{2\pi R_{3} C_{1}}$$

Figure 49. Frequency Response of Simple Low-pass Active Filter in Figure 9

$f_c$

f (log)

Note that the single-op-amp active filters are used in to the applications that require low quality factor, Q ( $\leq$  10), low frequency ( $\leq$  5 kHz), and low gain ( $\leq$  10), or a small value for the product of gain times Q ( $\leq$  100). The op amp should have an open loop voltage gain at the highest frequency of interest at least 50 times larger than the gain of the filter at this frequency. In addition, the selected op amp should have a slew rate that meets the following requirement:

Slew Rate  $\geq 0.5 \text{ x } (\omega_H \text{V}_{OPP}) \text{ X } 10^{-6} \text{V/}\mu\text{sec}$

### where

ω<sub>H</sub> is the highest frequency of interest

V<sub>OPP</sub> is the output peak-to-peak voltage

(6)

## SNOS413D - AUGUST 2000 - REVISED MARCH 2013

## **REVISION HISTORY**

| Changes from Revision C (March 2013) to Revision D |                                                    |  |    |  |  |

|----------------------------------------------------|----------------------------------------------------|--|----|--|--|

| •                                                  | Changed layout of National Data Sheet to TI format |  | 15 |  |  |

11-Apr-2013

## **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

| LPV321M5         | ACTIVE | SOT-23       | DBV                | 5    | 1000           | TBD                        | Call TI          | Call TI            | -40 to 85    | A27A              | Samples |

| LPV321M5/NOPB    | ACTIVE | SOT-23       | DBV                | 5    | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | A27A              | Samples |

| LPV321M5X        | ACTIVE | SOT-23       | DBV                | 5    | 3000           | TBD                        | Call TI          | Call TI            | -40 to 85    | A27A              | Samples |

| LPV321M5X/NOPB   | ACTIVE | SOT-23       | DBV                | 5    | 3000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | A27A              | Samples |

| LPV321M7         | ACTIVE | SC70         | DCK                | 5    | 1000           | TBD                        | Call TI          | Call TI            | -40 to 85    | A19               | Samples |

| LPV321M7/NOPB    | ACTIVE | SC70         | DCK                | 5    | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | A19               | Samples |

| LPV321M7X        | ACTIVE | SC70         | DCK                | 5    | 3000           | TBD                        | Call TI          | Call TI            | -40 to 85    | A19               | Samples |

| LPV321M7X/NOPB   | ACTIVE | SC70         | DCK                | 5    | 3000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | A19               | Samples |

| LPV324M          | ACTIVE | SOIC         | D                  | 14   | 55             | TBD                        | Call TI          | Call TI            | -40 to 85    | LPV324M           | Samples |

| LPV324M/NOPB     | ACTIVE | SOIC         | D                  | 14   | 55             | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LPV324M           | Samples |

| LPV324MT         | ACTIVE | TSSOP        | PW                 | 14   | 94             | TBD                        | Call TI          | Call TI            | -40 to 85    | LPV324<br>MT      | Samples |

| LPV324MT/NOPB    | ACTIVE | TSSOP        | PW                 | 14   | 94             | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LPV324<br>MT      | Samples |

| LPV324MTX        | ACTIVE | TSSOP        | PW                 | 14   | 2500           | TBD                        | Call TI          | Call TI            | -40 to 85    | LPV324<br>MT      | Samples |

| LPV324MTX/NOPB   | ACTIVE | TSSOP        | PW                 | 14   | 2500           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LPV324<br>MT      | Samples |

| LPV324MX         | ACTIVE | SOIC         | D                  | 14   | 2500           | TBD                        | Call TI          | Call TI            | -40 to 85    | LPV324M           | Samples |

| LPV324MX/NOPB    | ACTIVE | SOIC         | D                  | 14   | 2500           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LPV324M           | Samples |

| LPV358M/NOPB     | ACTIVE | SOIC         | D                  | 8    | 95             | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM |              | LPV<br>358M       | Samples |

| LPV358MM         | ACTIVE | VSSOP        | DGK                | 8    | 1000           | TBD                        | Call TI          | Call TI            | -40 to 85    | P358              | Samples |

www.ti.com

## PACKAGE OPTION ADDENDUM

11-Apr-2013

| Orderable Device | Status | Package Type | _       | Pins | _    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                        |                  | (3)                |              | (4)               |         |

| LPV358MM/NOPB    | ACTIVE | VSSOP        | DGK     | 8    | 1000 | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | P358              | Samples |

| LPV358MMX        | ACTIVE | VSSOP        | DGK     | 8    | 3500 | TBD                        | Call TI          | Call TI            | -40 to 85    | P358              | Samples |

| LPV358MMX/NOPB   | ACTIVE | VSSOP        | DGK     | 8    | 3500 | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | P358              | Samples |

| LPV358MX         | ACTIVE | SOIC         | D       | 8    | 2500 | TBD                        | Call TI          | Call TI            | -40 to 85    | LPV<br>358M       | Samples |

| LPV358MX/NOPB    | ACTIVE | SOIC         | D       | 8    | 2500 | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LPV<br>358M       | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

11-Apr-2013

## PACKAGE MATERIALS INFORMATION

www.ti.com 8-Apr-2013

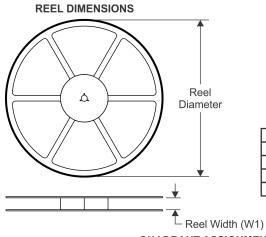

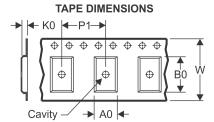

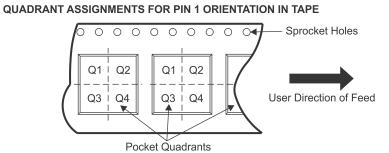

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

- Reel Width (W1)

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LPV321M5       | SOT-23          | DBV                | 5    | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LPV321M5/NOPB  | SOT-23          | DBV                | 5    | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LPV321M5X      | SOT-23          | DBV                | 5    | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LPV321M5X/NOPB | SOT-23          | DBV                | 5    | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LPV321M7       | SC70            | DCK                | 5    | 1000 | 178.0                    | 8.4                      | 2.25       | 2.45       | 1.2        | 4.0        | 8.0       | Q3               |

| LPV321M7/NOPB  | SC70            | DCK                | 5    | 1000 | 178.0                    | 8.4                      | 2.25       | 2.45       | 1.2        | 4.0        | 8.0       | Q3               |

| LPV321M7X      | SC70            | DCK                | 5    | 3000 | 178.0                    | 8.4                      | 2.25       | 2.45       | 1.2        | 4.0        | 8.0       | Q3               |

| LPV321M7X/NOPB | SC70            | DCK                | 5    | 3000 | 178.0                    | 8.4                      | 2.25       | 2.45       | 1.2        | 4.0        | 8.0       | Q3               |

| LPV324MTX      | TSSOP           | PW                 | 14   | 2500 | 330.0                    | 12.4                     | 6.95       | 8.3        | 1.6        | 8.0        | 12.0      | Q1               |

| LPV324MTX/NOPB | TSSOP           | PW                 | 14   | 2500 | 330.0                    | 12.4                     | 6.95       | 8.3        | 1.6        | 8.0        | 12.0      | Q1               |

| LPV324MX       | SOIC            | D                  | 14   | 2500 | 330.0                    | 16.4                     | 6.5        | 9.35       | 2.3        | 8.0        | 16.0      | Q1               |

| LPV324MX/NOPB  | SOIC            | D                  | 14   | 2500 | 330.0                    | 16.4                     | 6.5        | 9.35       | 2.3        | 8.0        | 16.0      | Q1               |

| LPV358MM       | VSSOP           | DGK                | 8    | 1000 | 178.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LPV358MM/NOPB  | VSSOP           | DGK                | 8    | 1000 | 178.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LPV358MMX      | VSSOP           | DGK                | 8    | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LPV358MMX/NOPB | VSSOP           | DGK                | 8    | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LPV358MX       | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LPV358MX/NOPB  | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

www.ti.com 8-Apr-2013

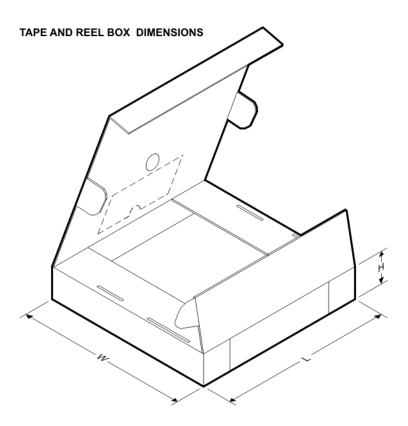

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LPV321M5       | SOT-23       | DBV             | 5    | 1000 | 210.0       | 185.0      | 35.0        |

| LPV321M5/NOPB  | SOT-23       | DBV             | 5    | 1000 | 210.0       | 185.0      | 35.0        |

| LPV321M5X      | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| LPV321M5X/NOPB | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| LPV321M7       | SC70         | DCK             | 5    | 1000 | 210.0       | 185.0      | 35.0        |

| LPV321M7/NOPB  | SC70         | DCK             | 5    | 1000 | 210.0       | 185.0      | 35.0        |

| LPV321M7X      | SC70         | DCK             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| LPV321M7X/NOPB | SC70         | DCK             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| LPV324MTX      | TSSOP        | PW              | 14   | 2500 | 367.0       | 367.0      | 35.0        |

| LPV324MTX/NOPB | TSSOP        | PW              | 14   | 2500 | 367.0       | 367.0      | 35.0        |

| LPV324MX       | SOIC         | D               | 14   | 2500 | 367.0       | 367.0      | 35.0        |

| LPV324MX/NOPB  | SOIC         | D               | 14   | 2500 | 367.0       | 367.0      | 35.0        |

| LPV358MM       | VSSOP        | DGK             | 8    | 1000 | 210.0       | 185.0      | 35.0        |

| LPV358MM/NOPB  | VSSOP        | DGK             | 8    | 1000 | 210.0       | 185.0      | 35.0        |

| LPV358MMX      | VSSOP        | DGK             | 8    | 3500 | 367.0       | 367.0      | 35.0        |

| LPV358MMX/NOPB | VSSOP        | DGK             | 8    | 3500 | 367.0       | 367.0      | 35.0        |

| LPV358MX       | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LPV358MX/NOPB  | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

# DBV (R-PDSO-G5)

## PLASTIC SMALL-OUTLINE PACKAGE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Falls within JEDEC MO-178 Variation AA.

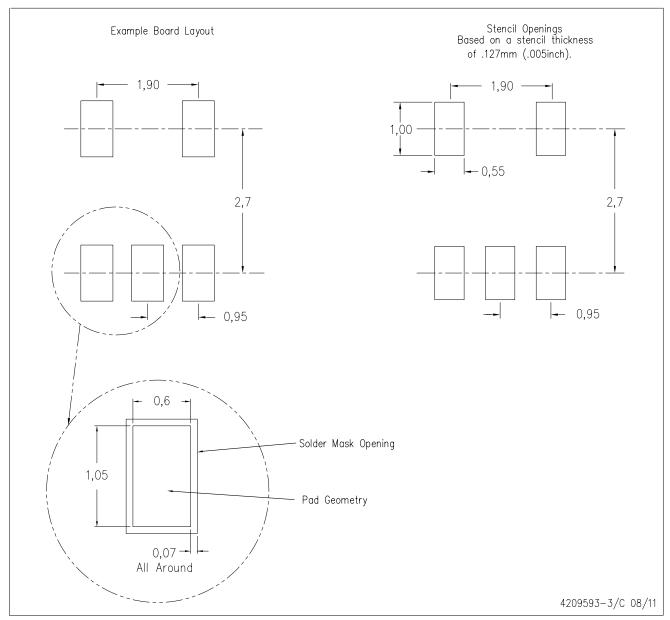

# DBV (R-PDSO-G5)

## PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

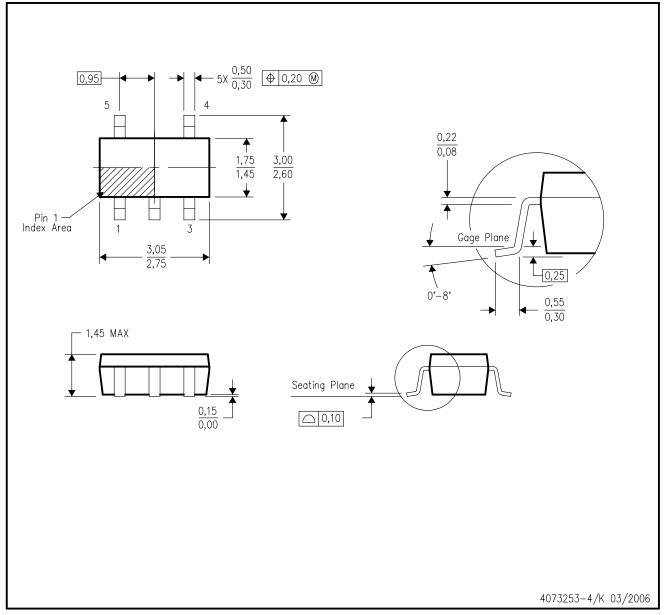

# DCK (R-PDSO-G5)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Falls within JEDEC MO-203 variation AA.

# DGK (S-PDSO-G8)

# PLASTIC SMALL-OUTLINE PACKAGE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

# D (R-PDSO-G14)

## PLASTIC SMALL OUTLINE

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AB.

PW (R-PDSO-G14)

## PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- Sody length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

- E. Falls within JEDEC MO-153

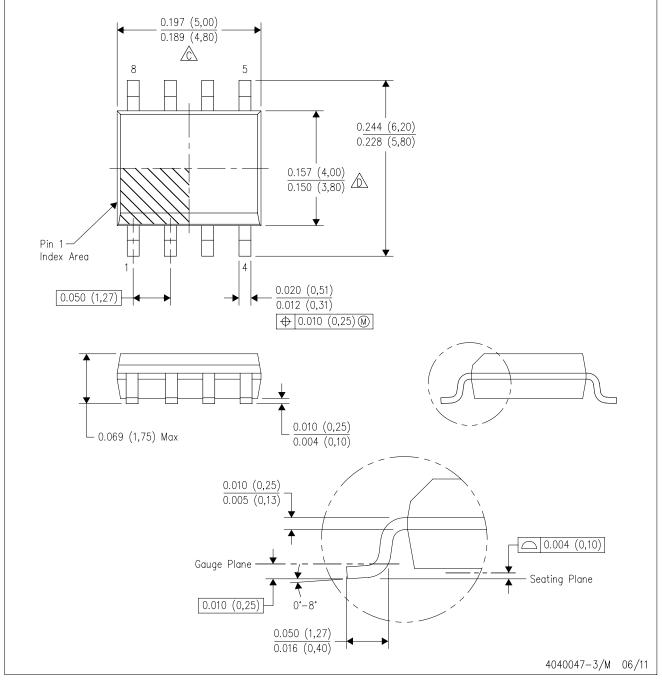

# D (R-PDSO-G8)

## PLASTIC SMALL OUTLINE

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="https://www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="https://example.com/omap">e2e.ti.com/omap</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>