TPA4411

SLOS430-AUGUST 2004

# 80-mW CAPLESS STEREO HEADPHONE DRIVER

### FEATURES

- Ground-Referenced Outputs Eliminate

DC-Bias Voltages on Headphone Ground Pin

- No Output DC-Blocking Capacitors

- Reduced Board Area

- Reduced Component Cost

- Improved THD+N Performance

- No Degradation of Low-Frequency Response Due to Output Capacitors

- Wide Power Supply Range: 1.8 V to 4.5 V

- 80-mW/Ch Output Power into 16-Ω at 4.5 V

- Independent Right and Left Channel Shutdown Control

- Short-Circuit and Thermal Protection

- Pop Reduction Circuitry

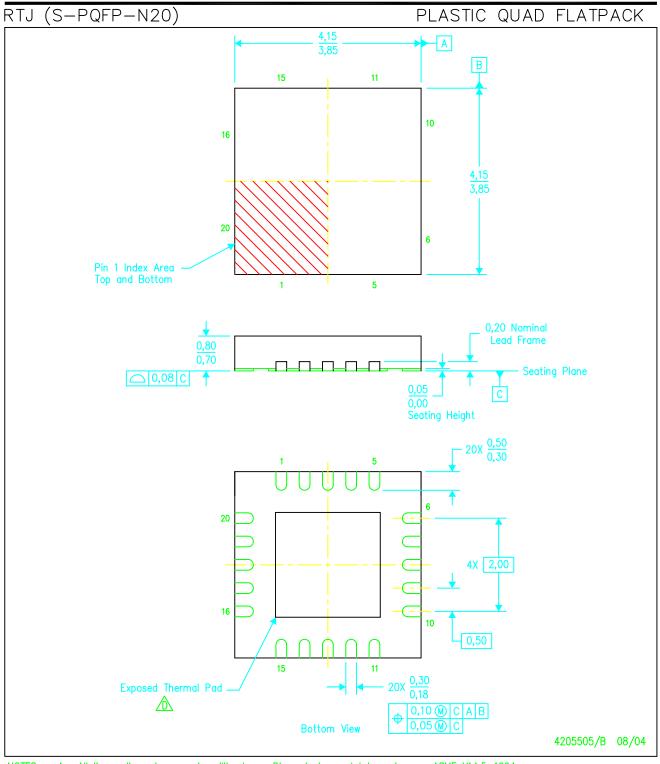

- Space Saving Pb-Free Packages - 20-pin, 4 mm × 4 mm ThinQFN

- 16-ball, 2 mm × 2 mm WCSP (Product Preview)

### APPLICATIONS

- Notebook Computers

- CD / MP3 Players

- Smart Phones

- Cellular Phones

- PDAs

### DESCRIPTION

The TPA4411 is a stereo headphone driver designed to allow the removal of the output dc-blocking capacitors for reduced component count and cost. The TPA4411 is ideal for small portable electronics where size and cost are critical design parameters.

The TPA4411 is capable of driving 80 mW into a 16- $\Omega$  load at 4.5 V. The TPA4411 has a fixed gain of -1.5 V/V and headphone outputs have  $\pm$ 8-kV IEC ESD protection. The TPA4411 has independent shutdown control for the right and left audio channels.

The TPA4411 is available in a 20-pin, 4 mm  $\times$  4 mm ThinQFN package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

A

# TPA4411

#### SLOS430-AUGUST 2004

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

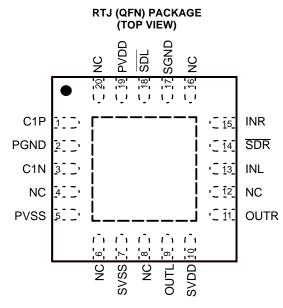

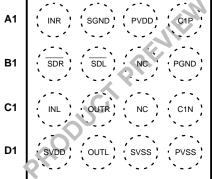

`(TOP VIEW) A2 A3 A4

YZH (WCSP) PACKAGE

NC - No internal connection

#### **TERMINAL FUNCTIONS**

| TERMINAL    |                        |                     | 10  |                                                                                      |

|-------------|------------------------|---------------------|-----|--------------------------------------------------------------------------------------|

| NAME        | QFN                    | WCSP <sup>(1)</sup> | 1/0 | DESCRIPTION                                                                          |

| C1P         | 1                      | A4                  | I/O | Charge pump flying capacitor positive terminal                                       |

| PGND        | 2                      | B4                  | I   | Power ground, connect to ground.                                                     |

| C1N         | 3                      | C4                  | I/O | Charge pump flying capacitor negative terminal                                       |

| NC          | 4, 6, 8, 12,<br>16, 20 | B3, C3              |     | No connection                                                                        |

| PVSS        | 5                      | D4                  | 0   | Output from charge pump.                                                             |

| SVSS        | 7                      | D3                  | I   | Amplifier negative supply, connect to PVSS via star connection.                      |

| OUTL        | 9                      | D2                  | 0   | Left audio channel output signal                                                     |

| SVDD        | 10                     | D1                  | I   | Amplifier positive supply, connect to PVDD via star connection.                      |

| OUTR        | 11                     | C2                  | 0   | Right audio channel output signal                                                    |

| INL         | 13                     | C1                  | I   | Left audio channel input signal                                                      |

| SDR         | 14                     | B1                  | I   | Right channel shutdown, active low logic.                                            |

| INR         | 15                     | A1                  | I   | Right audio channel input signal                                                     |

| SGND        | 17                     | A2                  | I   | Signal ground, connect to ground.                                                    |

| SDL         | 18                     | B2                  | I   | Left channel shutdown, active low logic.                                             |

| PVDD        | 19                     | A3                  | I   | Supply voltage, connect to positive supply.                                          |

| Exposed Pad |                        | -                   |     | Exposed pad must be soldered to a floating plane. Do NOT connect to power or ground. |

(1) Package not yet available

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range,  $T_A = 25^{\circ}C$  (unless otherwise noted)

|                  |                                                              |                               | UNIT |

|------------------|--------------------------------------------------------------|-------------------------------|------|

|                  | Supply voltage, AVDD, PVDD                                   | -0.3 to 5.5                   | V    |

| VI               | Input voltage                                                | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                  | Output Continuous total power dissipation                    | See Dissipation Rating Tab    | le   |

| T <sub>A</sub>   | Operating free-air temperature range                         | - 40 to 85                    | °C   |

| TJ               | Operating junction temperature range                         | - 40 to 150                   | °C   |

| T <sub>stg</sub> | Storage temperature range                                    | -65 to 85                     | °C   |

|                  | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260                           | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **DISSIPATION RATINGS TABLE**

| PACKAGE            | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR <sup>(1)</sup> | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|--------------------|---------------------------------------|--------------------------------|---------------------------------------|---------------------------------------|

| RTJ                | 3450 mW                               | 34.5 mW/°C                     | 1898 mW                               | 1380 mW                               |

| YZH <sup>(2)</sup> | TBD                                   | TBD mW/°C                      | TBD                                   | TBD                                   |

(1) Derating factor measured with High K board.

(2) Product preview

#### **AVAILABLE OPTIONS**

| T <sub>A</sub> | PACKAGED DEVICES                | PART NUMBER               | SYMBOL |

|----------------|---------------------------------|---------------------------|--------|

| -40°C to 85°C  | 20-pin, 4 mm $\times$ 4 mm QFN  | TPA4411RTJ <sup>(1)</sup> | AKQ    |

| -40°C 10 85°C  | 16-ball, 2 mm $\times$ 2mm WSCP | TPA4411YZH                | AKT    |

(1) The RTJ package is only available taped and reeled. To order, add the suffix "R" to the end of the part number for a reel of 3000, or add the suffix "T" to the end of the part number for a reel of 250 (e.g., TPA4411RTJR).

### **RECOMMENDED OPERATING CONDITIONS**

|                 |                                |          | MIN  | МАХ                | UNIT |

|-----------------|--------------------------------|----------|------|--------------------|------|

|                 | Supply voltage, AVDD, PVDD     |          | 1.8  | 4.5 <sup>(1)</sup> | V    |

| VIH             | High-level input voltage       | SDL, SDR | 1.5  |                    | V    |

| V <sub>IL</sub> | Low-level input voltage        | SDL, SDR |      | 0.5                | V    |

| T <sub>A</sub>  | Operating free-air temperature |          | - 40 | 85                 | °C   |

(1) Device can shut down for VDD > 4.5 V to prevent damage to the device.

### **ELECTRICAL CHARACTERISTICS**

$T_A = 25^{\circ}C$  (unless otherwise noted)

|                 | PARAMETER                           | TEST CONDITIONS                                                                                   | MIN | ТҮР | MAX  | UNIT |

|-----------------|-------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|------|------|

| IVOSI           | Output offset voltage               | $V_{DD}$ = 1.8 V to 4.5 V, Inputs grounded                                                        |     |     | 8    | mV   |

| PSRR            | Power Supply Rejection Ratio        | $V_{DD} = 1.8 V \text{ to } 4.5 V$                                                                | -69 | -80 |      | dB   |

| V <sub>OH</sub> | High-level output voltage           | $V_{DD}$ = 3 V, R <sub>L</sub> = 16 $\Omega$                                                      | 2.2 |     |      | V    |

| V <sub>OL</sub> | Low-level output voltage            | $V_{DD} = 3 \text{ V}, \text{ R}_{L} = 16 \Omega$                                                 |     |     | -1.1 | V    |

| I <sub>IH</sub> | High-level input current (SDL, SDR) | $V_{DD} = 4.5 \text{ V}, \text{ V}_{I} = V_{DD}$                                                  |     |     | 1    | μA   |

| I <sub>IL</sub> | Low-level input current (SDL, SDR)  | $V_{DD} = 4.5 V, V_I = 0 V$                                                                       |     |     | 1    | μA   |

|                 |                                     | $V_{DD} = 1.8 \text{ V}$ , No load, $\overline{\text{SDL}} = \overline{\text{SDR}} = V_{DD}$      |     | 5.3 | 6.5  |      |

| I <sub>DD</sub> | Supply Current                      | $V_{DD} = 3 \text{ V}$ , No load, $\overline{SDL} = \overline{SDR} = V_{DD}$                      |     | 6.5 | 8.0  | mA   |

|                 |                                     | $V_{DD} = 4.5 \text{ V}, \text{ No load}, \overline{\text{SDL}} = \overline{\text{SDR}} = V_{DD}$ |     | 8.0 | 10.0 |      |

|                 |                                     | Shutdown mode, $V_{DD}$ = 1.8 V to 4.5 V                                                          |     |     | 1    | μA   |

### **OPERATING CHARACTERISTICS**

$V_{\text{DD}}$  = 3 V ,  $T_{\text{A}}$  = 25°C,  $R_{\text{L}}$  = 16  $\Omega$  (unless otherwise noted)

|                  | PARAMETER                       | TEST CONDITIONS                                                      | MIN   | TYP    | MAX   | UNIT              |  |

|------------------|---------------------------------|----------------------------------------------------------------------|-------|--------|-------|-------------------|--|

|                  |                                 | THD = 1%, V <sub>DD</sub> = 3 V, f = 1 kHz                           |       | 50     |       |                   |  |

| Po               | Output power (Outputs In Phase) | THD = 1%, V <sub>DD</sub> = 4.5 V, f = 1 kHz                         |       | 80     |       | mW                |  |

|                  |                                 | THD = 1%, $V_{DD}$ = 3 V, f = 1 kHz,<br>R <sub>L</sub> = 32 $\Omega$ |       | 40     |       |                   |  |

|                  | Total harmonic distortion plus  | P <sub>O</sub> = 25 mW, f = 1 kHz                                    |       | 0.054% |       |                   |  |

| THD+N            | noise                           | P <sub>O</sub> = 25 mW, f = 20 kHz                                   |       | 0.010% |       |                   |  |

| Crosstallk       |                                 | P <sub>O</sub> = 20 mW, f = 1 kHz                                    |       | -83    |       | dB                |  |

|                  |                                 | 200-mV <sub>pp</sub> ripple, f = 217 Hz                              |       | -82.5  |       |                   |  |

| k <sub>SVR</sub> | Supply ripple rejection ratio   | 200-mV <sub>pp</sub> ripple, f = 1 kHz                               |       | -70.4  |       | dB                |  |

|                  |                                 | 200-mV <sub>pp</sub> ripple, f = 20 kHz                              |       | -45.1  |       |                   |  |

| A <sub>v</sub>   | Closed-loop voltage gain        |                                                                      | -1.45 | -1.5   | -1.55 | V/V               |  |

| $\Delta A_v$     | Gain matching                   |                                                                      |       | 1%     |       |                   |  |

|                  | Slew rate                       |                                                                      |       | 2.2    |       | V/µs              |  |

|                  | Maximum capacitive load         |                                                                      |       | 400    |       | pF                |  |

| V <sub>n</sub>   | Noise output voltage            |                                                                      |       | 10     |       | μV <sub>RMS</sub> |  |

|                  | Electrostatic discharge, IEC    | OUTR, OUTL                                                           |       | ±8     |       | kV                |  |

| f <sub>osc</sub> | Charge pump switching frequency |                                                                      | 280   | 320    | 420   | kHz               |  |

|                  | Start-up time from shutdown     |                                                                      |       | 450    |       | μs                |  |

|                  | Input impedance                 |                                                                      | 12    | 15     | 18    | kΩ                |  |

| SNR              | Signal-to-noise ratio           | P <sub>o</sub> = 40 mW (THD+N = 0.1%)                                |       | 98     |       | dB                |  |

|                  |                                 | Threshold                                                            | 150   |        | 170   | °C                |  |

|                  | Thermal shutdown                | Hysteresis                                                           |       | 15     |       | °C                |  |

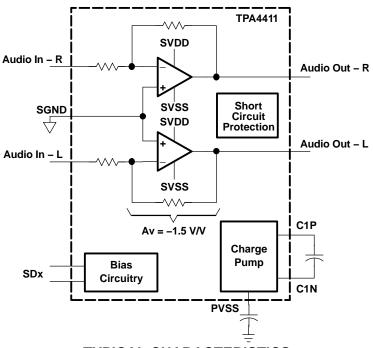

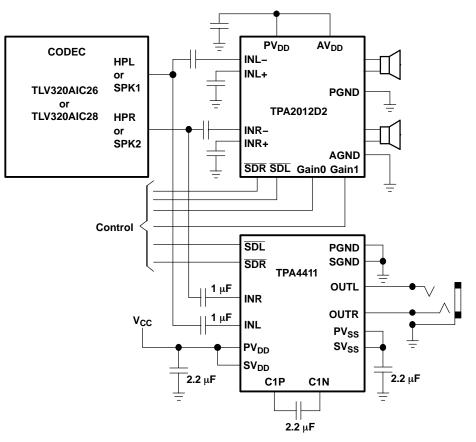

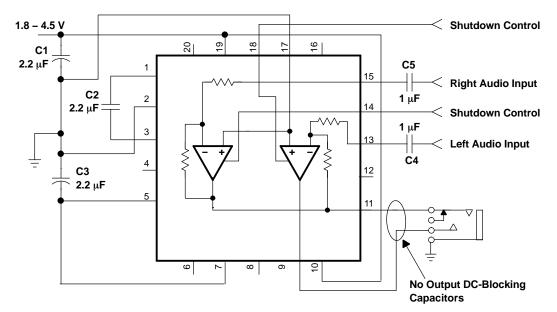

**Functional Block Diagram**

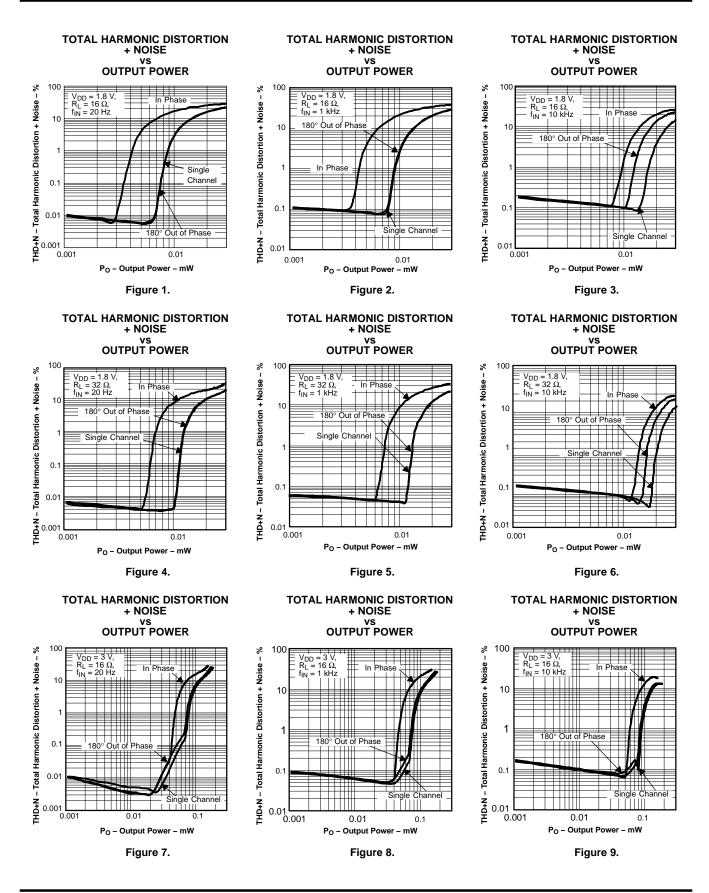

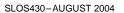

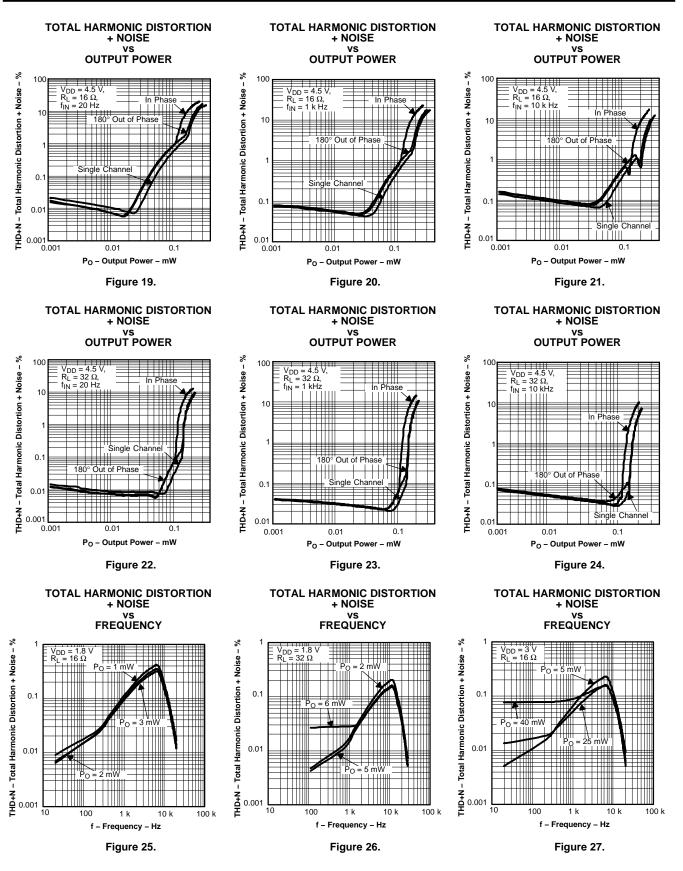

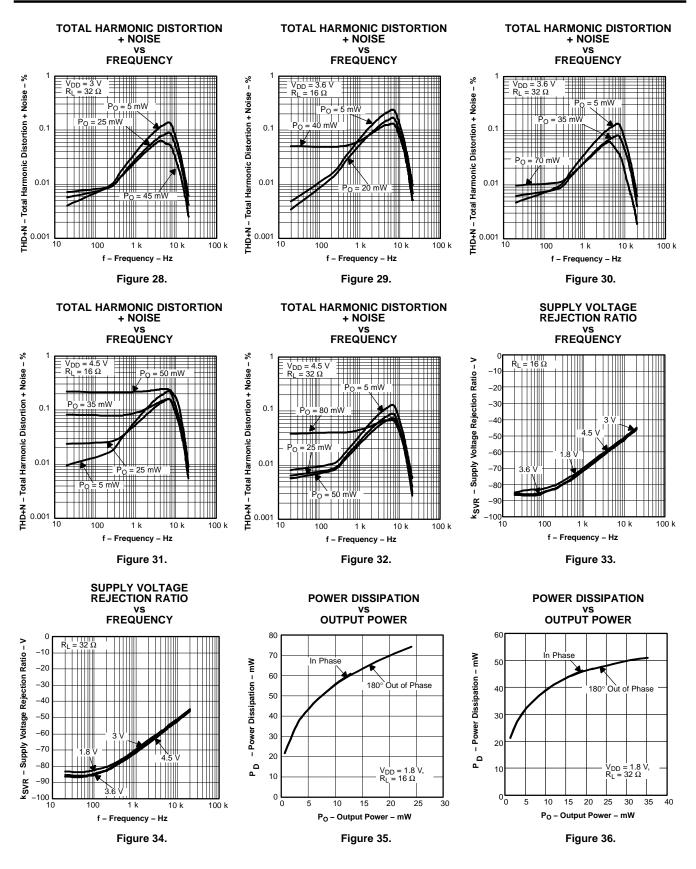

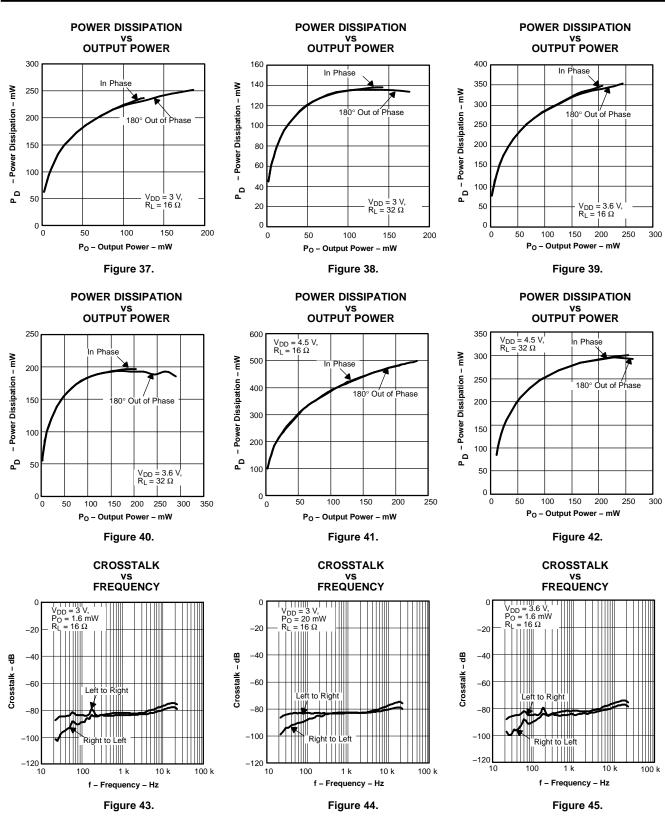

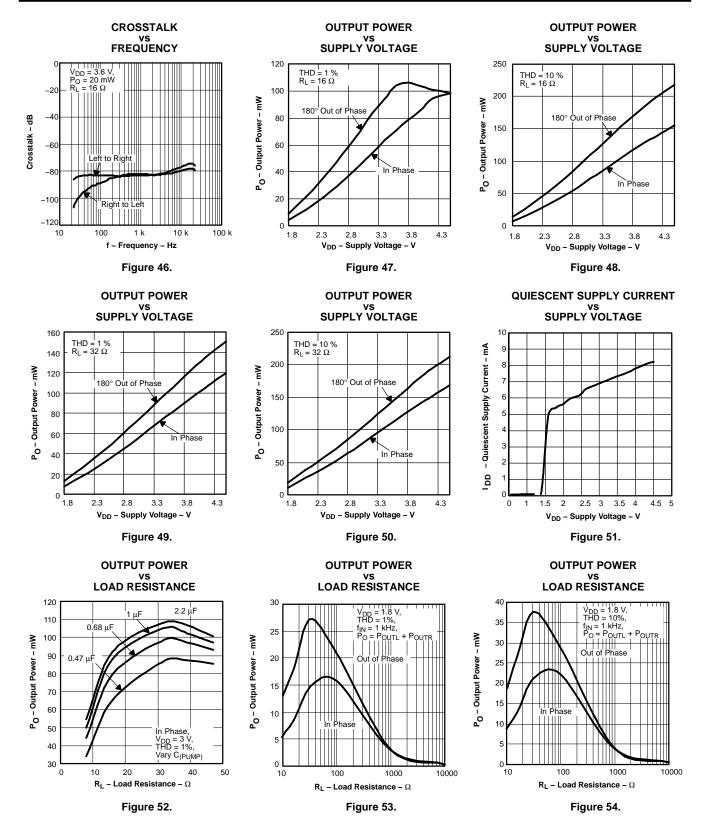

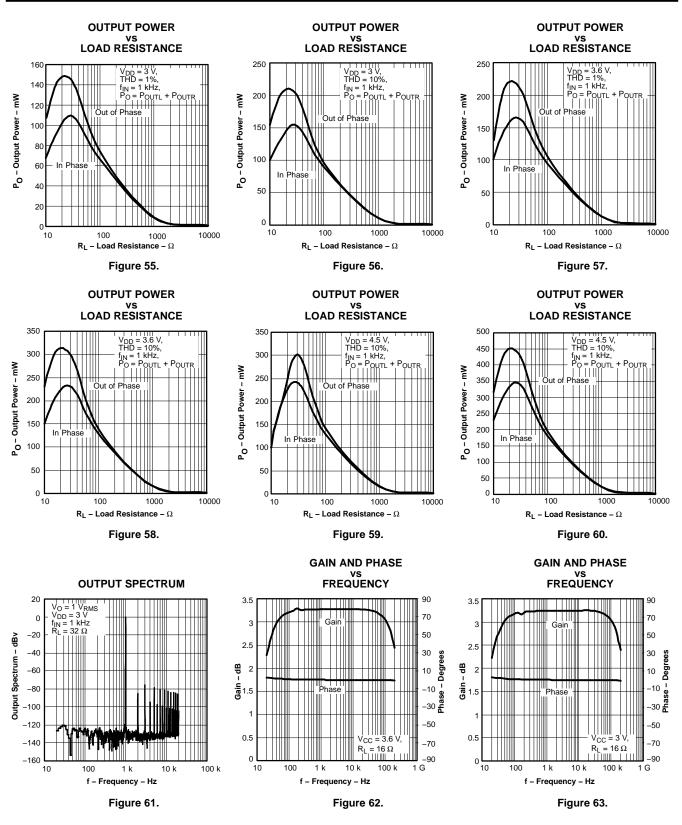

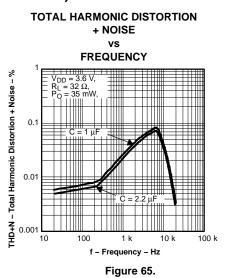

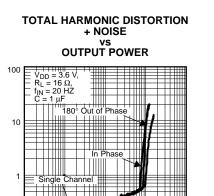

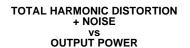

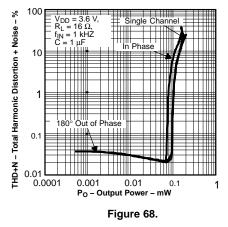

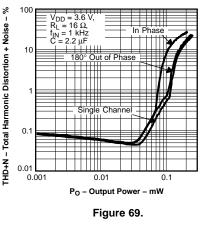

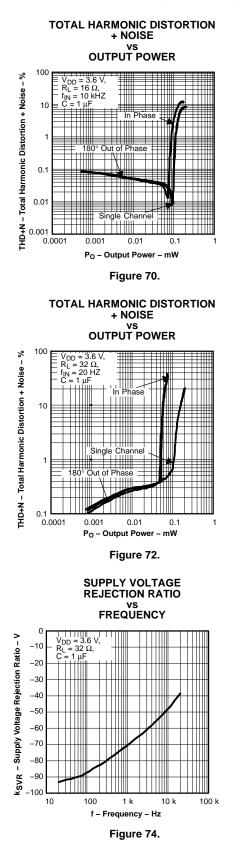

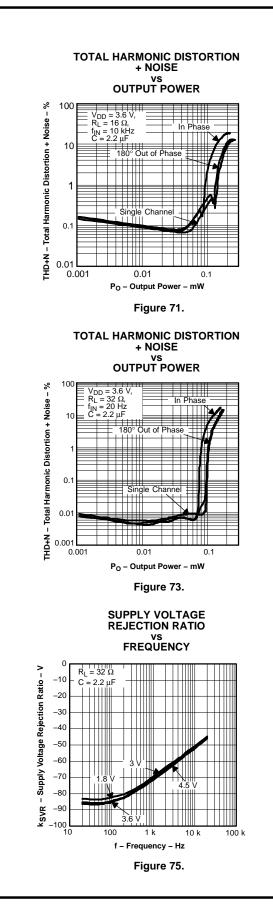

### **TYPICAL CHARACTERISTICS**

$C_{(\text{PUMP})}$  =  $C_{(\text{PVSS})}$  = 2.2  $\mu\text{F}$  ,  $C_{\text{IN}}$  = 1  $\mu\text{F}$  (unless otherwise noted)

### **Table of Graphs**

|                                   |                    | FIGURE  |

|-----------------------------------|--------------------|---------|

| Total harmonic distortion + noise | vs Output power    | 1 - 24  |

| Total harmonic distortion + noise | vs Frequency       | 25 - 32 |

| Supply voltage rejection ratio    | vs Frequency       | 33, 34  |

| Power dissipation                 | vs Output power    | 35 - 42 |

| Crosstalk                         | vs Frequency       | 43 - 46 |

| Output power                      | vs Supply voltage  | 47 - 50 |

| Quiescent supply current          | vs Supply voltage  | 51      |

| Output power                      | vs Load resistance | 52 - 60 |

| Output spectrum                   |                    | 61      |

| Gain and phase                    | vs Frequency       | 62, 63  |

#### TEXAS INSTRUMENTS www.ti.com

### **APPLICATION INFORMATION**

#### **Headphone Amplifiers**

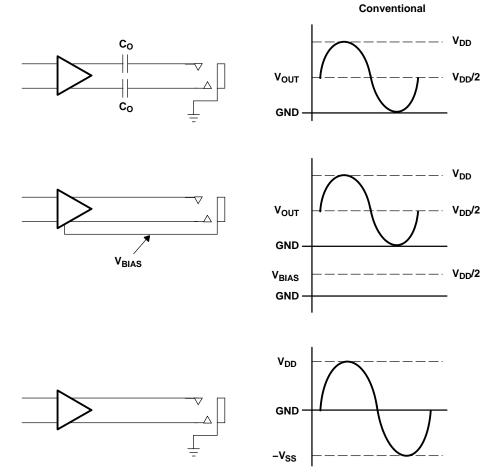

For single-supply headphone amplifiers, the output architecture typically require dc-blocking capacitors to remove the mid-rail bias required to obtain symmetrical output voltage swing. These capacitors are required because most headphone jacks are ground-referenced, with respect to the shield pin. Without the capacitors, there would be a dc bias voltage across the headphone speakers. In Figure 64, the first block diagram and waveform illustrate the traditional headphone amplifier connection to the headphone jack and output signal.

These capacitors are typically large in value in order to prevent the filtering of the output audio signal. The dc-blocking capacitors form a high-pass filter with the load impedance of the headphone speakers. Treating the headphone speakers as a resistive load, typically either  $16\Omega$  or  $32 \Omega$ , the dc-blocking capacitors form a high-pass filter with the load impedance. Equation 1 shows the relationship between the load impedance (R), the capacitor (C), and the cutoff frequency.

$$f = \frac{1}{2\pi R C}$$

(1)

Substituting for the values in the circuit, the dc-blocking capacitors can be determined using Equation 2, where the load impedance and the cutoff frequency are known.

$$C_{O} = \frac{1}{2\pi R_{L} f c_{OUT}}$$

(2)

From Equation 2, the capacitor must have a large value because the resistance value is small. Large capacitance values require large package sizes which consume board area, increase cost of the assembly, and can reduce the fidelity of the audio output signal.

Two different capless headphone amplifier applications are available that allow for the removal of the output dc-blocking capacitors. The first amplifier architecture is implemented in the same manner as the traditional amplifier with the exception of the headphone jack shield pin. This amplifier provides a reference voltage, which is connected to the headphone jack shield pin. This is the voltage on which the audio output signals are centered. This voltage reference is typically half of the amplifier power supply because this allows symmetrical swing of the output voltages. The second block diagram and waveform shows the mid-supply biased capless headphone architecture.

The second amplifier architecture operates from a single supply but makes use of an internal charge pump to provide a negative voltage rail. Using this negative supply, the headphone amplifier is now a split supply amplifier (internally) and can be considered a ground-reference amplifier. The output voltages are now centered at zero volts with the capability to swing to the positive rail or negative rail. The bottom block diagram and waveform of Figure 64 illustrate the ground-referenced capless headphone architecture.

#### **Input-Blocking Capacitors**

DC input-blocking capacitors are required to be added in series with the audio signal into the input pins of the TPA4411. These capacitors block the dc portion of the audio source and allow the TPA4411 inputs to be properly biased to provide maximum performace.

These capacitors form a high-pass filter with the input impedance of the TPA4411. The cutoff frequency is calculated using Equation 1. For this calculation, the capacitance used is input-blocking capacitor and the resistance is the input impedance of the TPA4411. Because the gain of the TPA4411 is fixed, the input impedance remains a constant value. Using the input impedance value from the operating characteristics table and Equation 2, the frequency and/or capacitance can be determined when one of the two values are given.

$$fc_{IN} = \frac{1}{2\pi R_{IN} C_{IN}} \quad \text{or} \quad C_{IN} = \frac{1}{2\pi fc_{IN} R_{IN}}$$

• Where  $R_{IN} = 15 \text{ k}\Omega$ .

(3)

### **APPLICATION INFORMATION (continued)**

Figure 64. Amplifier Applications

#### **Charge Pump Flying Capacitor and PVSS Capacitor**

The charge pump flying capacitor serves to transfer charge during the generation of the negative supply voltage. The PVSS capacitor must be at least equal to the charge pump capacitor in order to allow maximum charge transfer. Low ESR capacitors are an ideal selection, and a value of 2.2  $\mu$ F is typical. Capacitor values that are smaller than 2.2  $\mu$ F can be used, but the maximum output power is reduced and the device may not operate to specifications. Figures 65 through 75 compare the performance of the TPA4411 with the recommended 2.2- $\mu$ F capacitors and 1- $\mu$ F capacitors.

THD+N – Total Harmonic Distortion + Noise – %

0.1

#### **APPLICATION INFORMATION (continued)**

0.001 0.01 0.1 P<sub>O</sub> – Output Power – mW 1

Figure 66.

DTAL HARMONIC DISTORTION + NOISE Statement St

Figure 67.

TOTAL HARMONIC DISTORTION + NOISE

vs OUTPUT POWER

#### **APPLICATION INFORMATION (continued)**

### **APPLICATION INFORMATION (continued)**

#### **Decoupling Capacitors**

The TPA4411 is a capless headphone amplifier that requires adequate power supply decoupling to ensure that the noise and total harmonic distortion (THD) are low. A good low equivalent-series-resistance (ESR) ceramic capacitor, typically 2.2  $\mu$ F, placed as close as possible to the device V<sub>DD</sub> lead works best. Placing this decoupling capacitor close to the TPA4411 is important for the performance of the amplifier. For filtering lower frequency noise signals, a 10- $\mu$ F or greater capacitor placed near the audio power amplifier would also help, but it is not required in most applications because of the high PSRR of this device.

#### Supply Voltage Limiting At 4.5 V

The TPA4411 has a built-in charge pump which serves to generate a negative rail for the headphone amplifier. Because the headphone amplifier operates from a positive voltage and negative voltage supply, circuitry has been implemented to protect the devices in the amplifier from an overvoltage condition. Once the supply is above 4.5 V, the TPA4411 can shut down in an overvoltage protection mode to prevent damage to the device. The TPA4411 resumes normal operation once the supply is reduced to 4.5 V or lower.

#### Layout Recommendations

#### Exposed Pad On TPA4411RTJ Package Option

The exposed metal pad on the TPA4411RTJ package must be soldered down to a pad on the PCB in order to maintain reliability. *The pad on the PCB should be allowed to float and not be connected to ground or power*. Connecting this pad to power or ground prevents the device from working properly because it is connected internally to PVSS.

#### **SGND and PGND Connections**

The SGND and PGND pins of the TPA4411 must be routed separately back to the decoupling capacitor in order to provide proper device operation. If the SGND and PGND pins are connected directly to each other, the part functions without risk of failure, but the noise and THD performance do not meet the specifications.

## **APPLICATION INFORMATION (continued)**

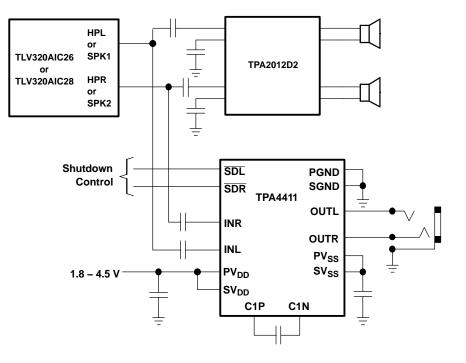

Figure 76. Application Circuit

Note: PowerPAD must be soldered down and plane must be floating.

Figure 77. Typical Circuit

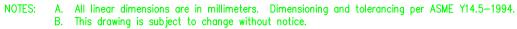

# **MECHANICAL DATA**

- В.

- С. QFN (Quad Flatpack No-Lead) package configuration.

- ightarrow The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

- B. This drawing is subject to change without notice.

- C. NanoFree™ package configuration.

- Devices in YZH package can have dimension D ranging from 1.85 to 2.65 mm and dimension E ranging from 1.85 to 2.65 mm.

To determine the exact package size of a particular device, refer to the device datasheet or contact a local TI representative.

Reference Product Data Sheet for array population.

- 4 x 4 matrix pattern is shown for illustration only.

- F. This package contains lead-free balls. Refer to YEH (Drawing #4204183) for tin-lead (SnPb) balls.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated