# **LMC7660 Switched Capacitor Voltage Converter**

## **General Description**

The LMC7660 is a CMOS voltage converter capable of converting a positive voltage in the range of  $\pm 1.5$ V to  $\pm 10$ V to the corresponding negative voltage of  $\pm 1.5$ V to  $\pm 10$ V. The LMC7660 is a pin-for-pin replacement for the industry-standard 7660. The converter features: operation over full temperature and voltage range without need for an external diode, low quiescent current, and high power efficiency.

The LMC7660 uses its built-in oscillator to switch 4 power MOS switches and charge two inexpensive electrolytic capacitors.

#### **Features**

- Operation over full temperature and voltage range without an external diode

- Low supply current, 200 µA max

- Pin-for-pin replacement for the 7660

- Wide operating range 1.5V to 10V

- 97% Voltage Conversion Efficiency

- 95% Power Conversion Efficiency

- Easy to use, only 2 external components

- Extended temperature range

- Narrow SO-8 Package

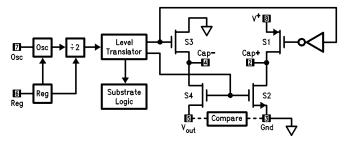

## **Block Diagram**

TL/H/9136-1

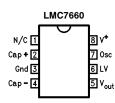

## **Pin Configuration**

#### **Ordering Information**

$$\begin{split} LMC7660MJ &-55^{\circ}C \leq T_{A} \leq +125^{\circ}C \\ LMC7660IN &-40^{\circ}C \leq T_{A} \leq +85^{\circ}C \\ LMC7660IM &-40^{\circ}C \leq T_{A} \leq +85^{\circ}C \end{split}$$

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage

Input Voltage on Pin 6, 7 (Note 2)

- 0.3V to (V  $^+$  + 0.3V) for  $V^+$  < 5.5V

(V  $^+$  - 5.5V) to (V  $^+$  + 0.3V) for  $V^+\,>\,5.5V$

20 μΑ

Continuous

Current into Pin 6 (Note 2)

Output Short Circuit Duration

$(\dot{V}^{+} \leq 5.5V)$

|                                  | Package<br>J N M                                             |            |            |  |  |  |

|----------------------------------|--------------------------------------------------------------|------------|------------|--|--|--|

| Power Dissipation (Note 3)       | 0.9W                                                         | 1.4W       | 0.8W       |  |  |  |

| T <sub>j</sub> Max (Note 3)      | 150°C                                                        | 150°C      | 150°C      |  |  |  |

| $\theta_{ja}$ (Note 3)           | 140°C/W                                                      | 90°C/W     | 160°C/W    |  |  |  |

| Storage Temp. Range              | $-65^{\circ}\text{C} \leq \text{T} \leq 150^{\circ}\text{C}$ |            |            |  |  |  |

| Lead Temp.<br>(Soldering, 5 sec) | 260°C                                                        | 260°C      | 260°C      |  |  |  |

| ESD Tolerance (Note 8)           |                                                              | $\pm2000V$ | $\pm2000V$ |  |  |  |

# **Electrical Characteristics** (Note 4)

| Symbol             | Parameter                             | Conditions                                                                | Тур        | LMC7660MJ                   | LMC7660IN/LMC7660IM         |                             |                 |

|--------------------|---------------------------------------|---------------------------------------------------------------------------|------------|-----------------------------|-----------------------------|-----------------------------|-----------------|

|                    |                                       |                                                                           |            | Tested<br>Limit<br>(Note 5) | Tested<br>Limit<br>(Note 5) | Design<br>Limit<br>(Note 6) | Units<br>Limits |

| Is                 | Supply Current                        | R <sub>L</sub> = ∞                                                        | 120        | 200<br><b>400</b>           | 200                         | 400                         | μA<br>max       |

| V <sup>+</sup> H   | Supply Voltage<br>Range High (Note 7) | $R_L = 10 \text{ k}\Omega$ , Pin 6 Open Voltage Efficiency $\geq 90\%$    | 3 to 10    | 3 to 10                     | 3 to 10                     | 3 to 10                     | ٧               |

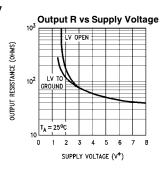

| V <sup>+</sup> L   | Supply Voltage<br>Range Low           | $R_L = 10 \text{ k}\Omega$ , Pin 6 to Gnd. Voltage Efficiency $\geq 90\%$ | 1.5 to 3.5 | 1.5 to 3.5                  | 1.5 to 3.5                  | 1.5 to 3.5                  | ٧               |

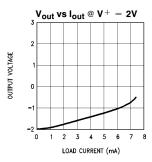

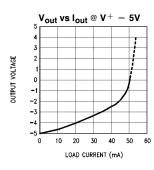

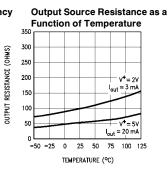

| R <sub>out</sub>   | Output Source<br>Resistance           | I <sub>L</sub> = 20 mA                                                    | 55         | 100<br><b>150</b>           | 100                         | 120                         | Ω<br>max        |

|                    |                                       | $V = 2V$ , $I_L = 3$ mA<br>Pin 6 Short to Gnd.                            | 110        | 200<br><b>300</b>           | 200                         | 300                         | Ω<br>max        |

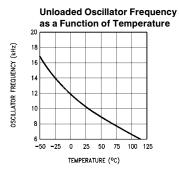

| F <sub>osc</sub>   | Oscillator<br>Frequency               |                                                                           | 10         |                             |                             |                             | kHz             |

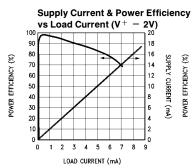

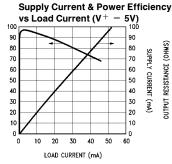

| P <sub>eff</sub>   | Power Efficiency                      | $R_L = 5 k\Omega$                                                         | 97         | 95<br><b>90</b>             | 95                          | 90                          | %<br>min        |

| V <sub>o eff</sub> | Voltage Conversion<br>Efficiency      | R <sub>L</sub> = ∞                                                        | 99.9       | 97<br><b>95</b>             | 97                          | 95                          | %<br>min        |

| I <sub>osc</sub>   | Oscillator Sink or<br>Source Current  | Pin 7 = Gnd. or V <sup>+</sup>                                            | 3          |                             |                             |                             | μΑ              |

Note 1: Absolute Maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions. See Note 4 for conditions.

Note 2: Connecting any input terminal to voltages greater than V+or less than ground may cause destructive latchup. It is recommended that no inputs from sources operating from external supplies be applied prior to "power-up" of the LMC7660.

Note 3: For operation at elevated temperature, these devices must be derated based on a thermal resistance of  $\theta_{ja}$  and  $T_j$  max,  $T_j = T_A + \theta_{ja} P_D$ .

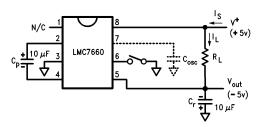

Note 4: Boldface numbers apply at temperature extremes. All other numbers apply at  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $C_{OSC} = 0$ , and apply for the LMC7660 unless otherwise specified. Test circuit is shown in Figure 1.

Note 5: Guaranteed and 100% production tested.

Note 6: Guaranteed over the operating temperature range (but not 100% tested). These limits are not used to calculate outgoing quality levels.

Note 7: The LMC7660 can operate without an external diode over the full temperature and voltage range. The LMC7660 can also be used with the external diode Dx, when replacing previous 7660 designs.

Note 8: The test circuit consists of the human body model of 100 pF in series with 1500  $\!\Omega.$

FIGURE 1. LMC7660 Test Circuit

TL/H/9136-5

## **Typical Performance Characteristics**

#### **CIRCUIT DESCRIPTION**

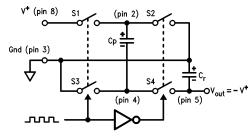

The LMC7660 contains four large CMOS switches which are switched in a sequence to provide supply inversion Vout -Vin. Energy transfer and storage are provided by two inexpensive electrolytic capacitors. Figure 2 shows how the LMC7660 can be used to generate  $-V^+$  from  $V^+$ . When switches S1 and S3 are closed, Cp charges to the supply voltage V+. During this time interval, switches S2 and S4 are open. After Cp charges to V+, S1 and S3 are opened, S2 and S4 are then closed. By connecting S2 to ground, Cp develops a voltage -V+/2 on Cr. After a number of cycles  $C_r$  will be pumped to exactly  $-V^+$ . This transfer will be exact assuming no load on C<sub>r</sub>, and no loss in the switches. In the circuit of Figure 2, S1 is a P-channel device and S2, S3, and S4 are N-channel devices. Because the output is biased below ground, it is important that the p- wells of S3 and S4 never become forward biased with respect to either their sources or drains. A substrate logic circuit guarantees that these p - wells are always held at the proper voltage. Under all conditions S4 p- well must be at the lowest potential in the circuit. To switch off S4, a level translator generates  $V_{GS4} = 0V$ , and this is accomplished by biasing the level translator from the S4 p - well.

An internal RC oscillator and  $\div$  2 circuit provide timing signals to the level translator. The built-in regulator biases the oscillator and divider to reduce power dissipation on high supply voltage. The regulator becomes active at about V+ = 6.5V. Low voltage operation can be improved if the LV pin is shorted to ground for V+  $\le$  3.5V. For V+  $\ge$  3.5V, the LV pin must be left open to prevent damage to the part.

#### **POWER EFFICIENCY AND RIPPLE**

It is theoretically possible to approach 100% efficiency if the following conditions are met:

- 1) The drive circuitry consumes little power.

- 2) The power switches are matched and have low Ron.

- The impedance of the reservoir and pump capacitors are negligibly small at the pumping frequency.

The LMC7660 closely approaches 1 and 2 above. By using a large pump capacitor  $C_p$ , the charge removed while supplying the reservoir capacitor is small compared to  $C_p$ 's total charge. Small removed charge means small changes in the pump capacitor voltage, and thus small energy loss and high efficiency. The energy loss by  $C_p$  is:

$$E = \frac{1}{2}C_{p} (V1^{2} - V2^{2})$$

By using a large reservoir capacitor, the output ripple can be reduced to an acceptable level. For example, if the load current is 5 mA and the accepted ripple is 200 mV, then the reservoir capacitor can omit approximately be calculated from:

$$\begin{split} \text{Is} &= C_{r} \frac{\text{d}v}{\text{d}t} \\ \sim & C_{r} \times \frac{V_{ripple\;p\text{-}p}}{\text{4/F}_{osc}} \quad C_{r} = \frac{0.5\;\text{mA}}{0.5\text{V/ms}} = 10\;\mu\text{F} \end{split}$$

#### **PRECAUTIONS**

- 1) Do not exceed the maximum supply voltage or junction temperature.

- 2) Do not short pin 6 (LV terminal) to ground for supply voltages greater than 3.5V.

- 3) Do not short circuit the output to V+.

- 4) External electrolytic capacitors  $C_{\rm r}$  and  $C_{\rm p}$  should have their polarities connected as shown in Figure 1.

#### **REPLACING PREVIOUS 7660 DESIGNS**

To prevent destructive latchup, previous 7660 designs require a diode in series with the output when operated at elevated temperature or supply voltage. Although this prevented the latchup problem of these designs, it lowered the available output voltage and increased the output series resistance.

The National LMC7660 has been designed to solve the inherent latch problem. The LCM7660 can operate over the

FIGURE 2. Idealized Voltage Converter

entire supply voltage and temperature range without the need for an output diode. When replacing existing designs, the LMC7660 can be operated with diode Dx.

## **Typical Applications**

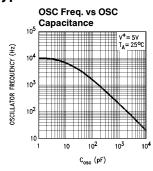

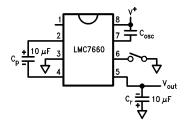

#### **Changing Oscillator Frequency**

It is possible to dramatically reduce the quiescent operating current of the LMC7660 by lowering the oscillator frequency. The oscillator frequency can be lowered from a nominal 10 kHz to several hundred hertz, by adding a slow-down capacitor  $C_{\rm OSC}$  (Figure 3). As shown in the Typical Performance Curves the supply current can be lowered to the 10  $\mu{\rm A}$  range. This low current drain can be extremely useful when

used in  $\mu Power$  and battery back-up equipment. It must be understood that the lower operating frequency and supply current cause an increased impedance of  $C_r$  and  $C_p$ . The increased impedance, due to a lower switching rate, can be offset by raising  $C_r$  and  $C_p$  until ripple and load current requirements are met.

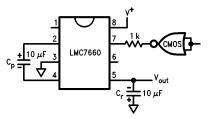

## Synchronizing to an External Clock

Figure 4 shows an LMC7660 synchronized to an external clock. The CMOS gate overrides the internal oscillator when it is necessary to switch faster or reduce power supply interference. The external clock still passes through the  $\div\,2$  circuit in the 7660, so the pumping frequency will be ½ the external clock frequency.

TL/H/9136-7

FIGURE 3. Reduce Supply Current by Lowering Oscillator Frequency

FIGURE 4. Synchronizing to an External Clock

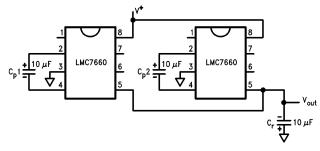

#### **Lowering Output Impedance**

Paralleling two or more LMC7660's lowers output impedance. Each device must have it's own pumping capacitor  $C_p$ , but the reservoir capacitor  $C_r$  is shared as depicted in *Figure 5*. The composite output resistance is:

composite output resistance is

$$R_{out} = \frac{R_{out} \text{ of one LMC7660}}{\text{Number of devices}}$$

#### **Increasing Output Voltage**

Stacking the LMC7660s is an easy way to produce a greater negative voltage. It should be noted that the input

current required for each stage is twice the load current on that stage as shown in Figure 6A. The effective output resistance is approximately the sum of the individual  $R_{\rm out}$  values, and so only a few levels of multiplication can be used. It is possible to generate -15V from +5V by connecting the second 7660's pin 8 to +5V instead of ground as shown in Figure 6B. Note that the second 7660 sees a full 20V and the input supply should not be increased beyond +5V

TL/H/9136-9

TL/H/9136-10

FIGURE 5. Lowering Output Resistance by Paralleling Devices

FIGURE 6A. Higher Voltage by Cascade

$C_{p} = +5V$   $C_{p} = +5V$

FIGURE 6B. Getting  $-\,$  15V from  $+\,$  5V

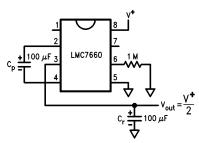

#### Split V+ In Half

Figure 7 is one of the more interesting applications for the LMC7660. The circuit can be used as a precision voltage divider (for very light loads), alternately it is used to generate a  $1\!\!/_2$  supply point in battery applications. In the  $1\!\!/_2$  cycle when S1 and S3 are closed, the supply voltage divides across the capacitors in a conventional way proportional to their value. In the  $1\!\!/_2$  cycle when S2 and S4 are closed, the capacitors switch from a series connection to a parallel connection. This forces the capacitors to have the same voltage; the charge redistributes to maintain precisely V+/2, across  $C_p$  and  $C_r$ . In this application all devices are only V+/2, and the supply voltage can be raised to 20V giving exactly 10V at Vout.

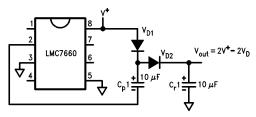

#### Getting Up . . . and Down

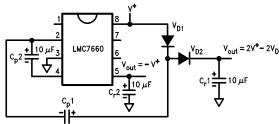

The LMC7660 can also be used as a positive voltage multiplier. This application, shown in Figure 8, requires 2 additional diodes. During the first  $1\!\!/_2$  cycle S2 charges  $C_p1$  through D1; D2 is reverse biased. In the next  $1\!\!/_2$  cycle S2 is open and S1 is closed. Since  $C_p1$  is charged to V+ - V $_{D1}$  and is referenced to V+ through S1, the junction of D1 and D2 is at V+ + (V+ - V $_{D1}$ ). D1 is reverse biased in this interval. This application uses only two of the four switches in the 7660. The other two switches can be put to use in performing a negative conversion at the same time as shown in Figure 9. In the  $1\!\!/_2$  cycle that D1 is charging  $C_p1$ ,  $C_p2$  is connected from ground to  $-V_{out}$  via S2 and S4, and  $C_r2$  is storing  $C_p2$ 's charge. In the interval that S1 and S3 are closed,  $C_p1$  pumps the junction of D1 and D2 above V+, while  $C_p2$  is refreshed from V+.

FIGURE 7. Split V+ in Half

TL/H/9136-12

FIGURE 8. Positive Voltage Multiplier

TL/H/9136-13

TL/H/9136-14

FIGURE 9. Combined Negative Converter and Positive Multiplier

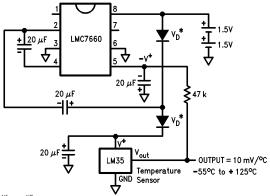

#### Thermometer Spans 180°C

Using the combined negative and positive multiplier of Figure 10 with an LM35 it is possible to make a  $\mu\text{Power}$  thermometer that spans a 180°C temperature range. The LM35 temperature sensor has an output sensitivity of 10 mV/°C, while drawing only 50  $\mu\text{A}$  of quiescent current. In order for the LM35 to measure negative temperatures, a pull down to a negative voltage is required. Figure 10 shows a thermometer circuit for measuring temperatures from  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and requiring only two 1.5V cells. End of battery life can be extended by replacing the up converter diodes with Schottky's.

#### Regulating - Vout

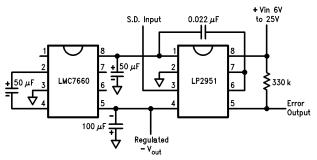

It is possible to regulate the output of the LMC7660 and still maintain  $\mu$ Power performance. This is done by enclosing

the LMC7660 in a loop with a LP2951. The circuit of Figure 11 will regulate  $V_{out}$  to -5 V for  $I_L=10$  mA, and  $V_{in}=6 V$ . For  $V_{in}>7 V$ , the output stays in regulation up to  $I_L=25$  mA. The error flag on pin 5 of the LP2951 sets low when the regulated output at pin 4 drops by about 5%. The LP2951 can be shutdown by taking pin 3 high; the LMC7660 can be shutdown by shorting pin 7 and pin 8.

The LP2951 can be reconfigured to an adjustable type regulator, which means the LMC7660 can give a regulated output from -2.0V to -10V dependent on the resistor ratios R1 and R2, as shown in Figure 12,  $V_{\text{ref}}=1.235V$ :

$$V_{out} = V_{ref} \left( 1 + \frac{R1}{R2} \right)$$

\*For lower voltage operation, use Schottky rectifiers

FIGURE 10.  $\mu$ Power Thermometer Spans 180°C, and Pulls Only 150  $\mu$ A

FIGURE 11. Regulated -5V with 200  $\mu\text{A}$  Standby Current

S.D. Input 0.022 µF + Vin 6V to 25V t

$V_{out} = V_{ref} \left( 1 + \frac{R1}{R2} \right)$   $V_{ref} = 1.235V$

\*Low voltage operation

FIGURE 12. LMC7660 and LP2951 Make a Negative Adjustable Regulator

TL/H/9136-16

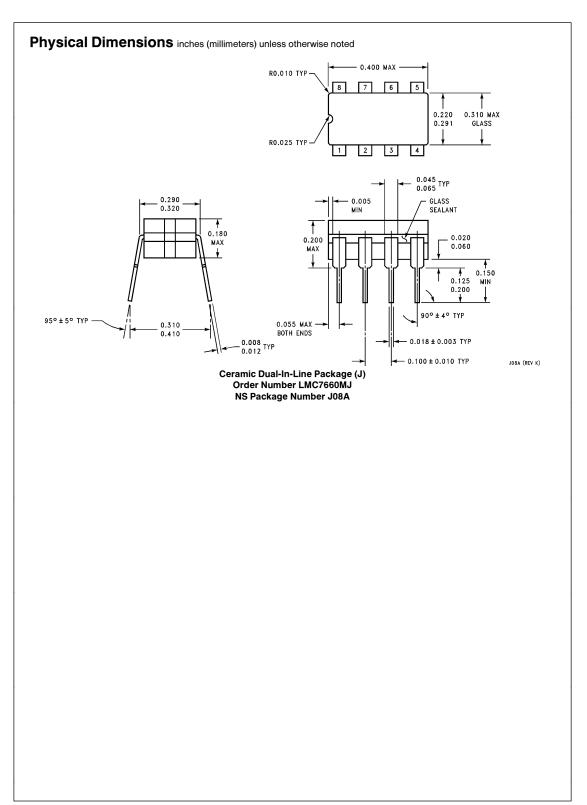

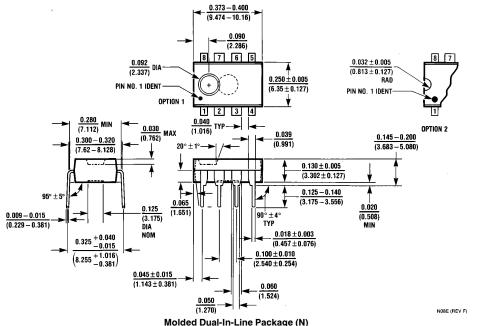

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

Molded Dual-In-Line Package (N) Order Number LMC7660IN NS Package Number N08E

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

http://www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Fax: +49 (0) 180-530 so so Email: europe.support@nsc.com Deutsch Tel: +49 (0) 180-530 85 85 English Tel: +49 (0) 180-532 78 32 Français Tel: +49 (0) 180-532 95 58 Italiano Tel: +49 (0) 180-534 16 80

National Semiconductor Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2308

Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications