Atmega128. Описание регистров TWI

Описание регистров TWI

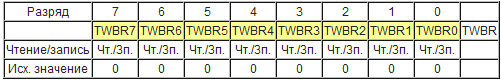

Регистр скорости связи шины TWI - TWBR

- Разряд 7..0 - Биты регистра скорости связи шины TWI

TWBR задает коэффициент деления частоты генератора скорости связи. Генератор частоты скорости связи - делитель частоты, который формирует сигнал синхронизации SCL в режимах "Ведущий". В разделе "Блок генератора скорости связи" показана методика вычисления скоростей связи.

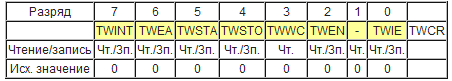

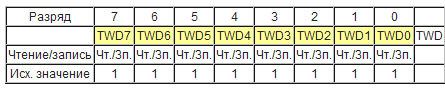

Регистр управления шиной TWI - TWCR

Регистр TWCR предназначен для управления работой TWI. Он используется для разрешения работы TWI, для инициации сеанса связи ведущего путем генерации условия СТАРТ на шине, для генерации подтверждения приема, для генерации условия СТОП и для останова шины во время записи в регистр TWDR. Он также сигнализирует о попытке ошибочной записи в регистр TWDR, когда доступ к нему был запрещен.

- Разряд 7 - TWINT: Флаг прерывания TWI

Данный бит устанавливается аппаратно, если TWI завершает текущее задание и ожидает реакции программы. Если бит I в SREG и бит TWIE в TWCR установлены, то микроконтроллер переходит на вектор прерывания TWI. Линия SCL остается в низком состоянии, пока установлен флаг TWINT. Флаг TWINT сбрасывается программно путем записи в него логической 1. Обратите внимание, что данный флаг сбрасывается не автоматически при переходе на вектор прерывания. Также нужно учесть, что очистка данного флага приводит к возобновлению работы TWI. Из этого следует, что программный сброс данного флага необходимо выполнить после завершения опроса регистров TWAR, TWSR и TWDR.

- Разряд 6 - TWEA: Бит разрешения подтверждения

Бит TWEA управляет генерацией импульса подтверждения. Если в бит TWEA записана лог. 1, то импульс ПОДТВ генерируется на шине TWI, если выполняется одно из следующих условий:

- Принят собственный подчиненный адрес.

- Принят общий вызов, когда установлен бит TWGCE в регистре TWAR.

- Принят байт данных в режиме ведущего приемника или подчиненного приемника.

Запись лог. 0 в бит TWEA позволяет временно отключиться от двухпроводной последовательной шины. Для возобновления распознавания адреса необходимо записать в данный бит лог.1.

- Разряд 5 - TWSTA: Бит условия СТАРТ

Программист должен установить данный бит при необходимости стать ведущим на двухпроводной последовательной шине. TWI аппаратно проверяет доступность шины и генерирует условие СТАРТ, если шина свободна. Однако если шина занята, то TWI ожидает появления условия СТОП, а затем генерирует новое условие СТАРТ для перехвата состояния ведущего шины. TWSTA необходимо сбрасывает программно после передачи условия СТАРТ.

- Разряд 4 - TWSTO: Бит условия СТОП

Установка бита TWSTO в режиме ведущего приводит к генерации условия СТОП на двухпроводной последовательной шине. Если на шине выполняется условие СТОП, то бит TWSTO сбрасывается автоматически. В подчиненном режиме установка бита TWSTO может использоваться для выхода из условия ошибки. В этом случае условие СТОП не генерируется, но интерфейс TWI возвращается к хорошо сконфигурированному безадресному подчиненному режиму и переводит линии SCL и SDA в высокоимпедансное состояние.

- Разряд 3 - TWWC: Флаг ошибочной записи

Бит TWWC устанавливается при попытке записи в регистр данных TWDR, когда TWINT имеет низкий уровень. Флаг сбрасывается при записи регистра TWDR, когда TWINT = 1.

- Разряд 2 - TWEN: Бит разрешения работы TWI

Бит TWEN разрешает работу TWI и активизирует интерфейс TWI. Если бит TWEN установлен, то TWI берет на себя функции управления линиями ввода-вывода SCL и SDA. При этом разрешается работа ограничителей скорости изменения фронтов и помехоподавляющих фильтров. Если данный бит равен нулю, то TWI отключается и все передачи прекращаются независимо от состояния работы.

- Разряд 1 - Резервный бит

Данный бит является резервным и считывается как 0.

- Разряд 0 - TWIE: Разрешение прерывания TWI

Если в данный бит записана лог. 1 и установлен бит I в регистре SREG, то запрос на прерывание TWI будет генерироваться до тех пор, пока установлен флаг TWINT.

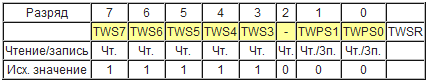

Регистр состояния TWI - TWSR

- Разряды 7..3 - TWS: Состояние TWI

Данные 5 бит отражают состояние логики блока TWI и двухпроводной последовательной шины. Различия в кодах состояния будут представлены далее в этом разделе. Обратите внимание, что считываемое значение из регистра TWSR содержит и 5-разр. код состояния и 2-разр. значение, управляющее предделителем. Программист должен маскировать к 0 биты предделителя во время проверки бит состояния. В этом случае проверка состояния не будет зависеть от настройки предделителя.

- Разряд 2 - Резервный бит

Данный бит является резервным и считывается как 0.

- Разряды 1..0 - TWPS: Биты предделителя TWI

Данные биты отличаются полным доступом (чтение/запись) и позволяют управлять предделителем скорости связи.

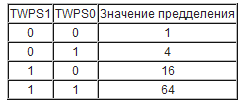

Таблица 87. Предделитель скорости связи TWI

Формула для вычисления скорости связи представлена в разделе "Блок генератора скорости связи". Значение бит TWPS1..0 используется в ней.

Регистр данных шины TWI - TWDR

В режиме передатчика регистр TWDR содержит следующий байт для передачи. В режиме приемника регистр TWDR содержит последний принятый байт. Запись в регистр возможна только когда TWI не выполняет процесс сдвига данных. Такое состояние наступает, когда происходит аппаратная установка флага прерывания TWINT. Обратите внимание, что регистр данных не может инициализироваться пользователем перед возникновением первого прерывания. Данные в регистре TWDR остаются стабильными пока установлен бит TWINT. Во время сдвига последовательной передачи данных одновременно происходит сдвиг для последовательного ввода. TWDR всегда содержит последний байт представленный на шине, исключая ситуацию возобновления нормальной работы микроконтроллера по прерыванию TWI. В этом случае состояние TWDR является неопределенным. В случае потери арбитрирования шины данные, передаваемые от ведущего к подчиненному, не теряются. Управление битом ПОДТВ происходит автоматически под управлением схемы TWI, а ЦПУ непосредственного доступа к биту ПОДТВ не имеет.

- Разряды 7..0 - TWD: Регистр данных шины TWI

Данные 8 бит составляют байт данных, который необходимо передать следующим, или последний принятый байт по двухпроводной последовательной шине.

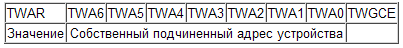

Регистр подчиненного адреса шины TWI - TWAR

Если TWI настроен на режим подчиненного передатчика или приемника, то будет реагировать только на адрес, записанный в этот регистр (в 7 старших разрядов TWAR). В остальных режимах ведущего данный регистр не используется. В многомастерных системах регистр TWAR устанавливается в том ведущем, к которому адресуются как к подчиненному другие ведущие шины.

Мл. разряд регистра TWAR используется для разрешения обнаружения адреса общего вызова ($00). Специальный компаратор выполняет сравнение подчиненного адреса (или адреса общего вызова) с принятым адресом. Если обнаруживается совпадение, то генерируется запрос на прерывание.

- Разряды 7..1 - TWA: Регистр подчиненного адреса TWI

Данные семь бит составляют подчиненный адрес блока TWI.

- Разряд 0 - TWGCE: Бит разрешения обнаружения общего вызова по шине TWI

После установки данного бита разрешается работа схемы обнаружения общего вызова, передаваемого по двухпроводной последовательной шине.

| << Предыдущая страница | Оглавление | Следующая страница >> |